XR17C158CV-F Exar Corporation, XR17C158CV-F Datasheet - Page 28

XR17C158CV-F

Manufacturer Part Number

XR17C158CV-F

Description

IC UART PCI BUS 5V OCTAL 144LQFP

Manufacturer

Exar Corporation

Type

Universal PCI Bus Octal UARTr

Datasheet

1.XR17C158CV-F.pdf

(67 pages)

Specifications of XR17C158CV-F

Number Of Channels

8

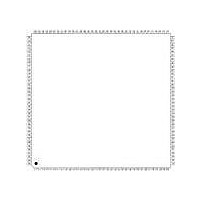

Package / Case

144-LQFP

Features

*

Fifo's

64 Byte

Protocol

RS485

Voltage - Supply

5V

With Auto Flow Control

Yes

With Irda Encoder/decoder

Yes

With False Start Bit Detection

Yes

With Modem Control

Yes

Mounting Type

Surface Mount

Data Rate

6.25 Mbps

Supply Voltage (max)

7 V

Supply Current

5 mA

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Mounting Style

SMD/SMT

Operating Supply Voltage

7 V

No. Of Channels

8

Uart Features

High Performance, Read/Write Burst Operation

Supply Voltage Range

-0.5V To 7V

Operating Temperature Range

0°C To +70°C

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

1016-1287

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XR17C158CV-F

Manufacturer:

Exar Corporation

Quantity:

10 000

Part Number:

XR17C158CV-F

Manufacturer:

EXAR/艾科嘉

Quantity:

20 000

XR17C158

5V PCI BUS OCTAL UART

The transmitter section comprises of a 64 bytes of FIFO, a byte-wide Transmit Holding Register (THR) and an

8-bit Transmit Shift Register (TSR). THR receives a data byte from the host (non-FIFO mode) or a data byte

from the FIFO when the FIFO is enabled by FCR bit-0. TSR shifts out every data bit with the 16X or 8X internal

clock. A bit time is 16 or 8 clock periods. The transmitter sends the start bit followed by the number of data bits,

inserts the proper parity bit if enabled, and adds the stop bit(s). The status of the THR and TSR are reported in

the Line Status Register (LSR bit-5 and bit-6).

The transmit holding register is an 8-bit register providing a data interface to the host processor. The host

writes transmit data byte to the THR to be converted into a serial data stream including start-bit, data bits,

parity-bit and stop-bit(s). The least-significant-bit (bit-0) becomes the first data bit to go out. The THR is also

the input register to the transmit FIFO of 64 bytes when FIFO operation is enabled by FCR bit-0. A THR empty

interrupt can be generated when it is enabled in IER bit-1.

The host loads transmit data to THR one character at a time. The THR empty flag (LSR bit-5) is set when the

data byte is transferred to TSR. THR flag can generate a transmit empty interrupt (ISR bit-1) when it is enabled

by IER bit-1. The TSR flag (LSR bit-6) is set when TSR becomes completely empty.

O

4.2

4.2.1

4.2.2

UTPUT

MCR Bit-7=1

T

230.4k

115.2k

19.2k

38.4k

57.6k

ABLE

1200

2400

4800

9600

100

600

Data Rate

Transmitter

Transmit Holding Register (THR) - Write-Only

Transmitter Operation in non-FIFO mode

9: T

YPICAL DATA RATES WITH A

O

UTPUT

MCR Bit-7=0

153.6k

230.4k

460.8k

921.6k

19.2k

38.4k

76.8k

2400

4800

9600

400

Data Rate

Clock (Decimal)

D

IVISOR FOR

2304

14.7456 MH

384

192

96

48

24

12

6

4

2

1

16x

D

28

IVISOR FOR

Z CRYSTAL OR EXTERNAL CLOCK AT

Clock (HEX)

900

180

C0

0C

60

30

18

06

04

02

01

16x

V

ALUE

P

ROGRAM

DLM

09

01

00

00

00

00

00

00

00

00

00

(HEX)

V

ALUE

P

ROGRAM

DLL

C0

0C

00

80

60

30

18

06

04

02

01

16X S

(HEX)

xr

AMPLING

D

E

REV. 1.4.3

ATA

RROR

0

0

0

0

0

0

0

0

0

0

0

R

ATE

(%)