XR17C158CV-F Exar Corporation, XR17C158CV-F Datasheet - Page 41

XR17C158CV-F

Manufacturer Part Number

XR17C158CV-F

Description

IC UART PCI BUS 5V OCTAL 144LQFP

Manufacturer

Exar Corporation

Type

Universal PCI Bus Octal UARTr

Datasheet

1.XR17C158CV-F.pdf

(67 pages)

Specifications of XR17C158CV-F

Number Of Channels

8

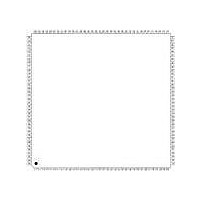

Package / Case

144-LQFP

Features

*

Fifo's

64 Byte

Protocol

RS485

Voltage - Supply

5V

With Auto Flow Control

Yes

With Irda Encoder/decoder

Yes

With False Start Bit Detection

Yes

With Modem Control

Yes

Mounting Type

Surface Mount

Data Rate

6.25 Mbps

Supply Voltage (max)

7 V

Supply Current

5 mA

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Mounting Style

SMD/SMT

Operating Supply Voltage

7 V

No. Of Channels

8

Uart Features

High Performance, Read/Write Burst Operation

Supply Voltage Range

-0.5V To 7V

Operating Temperature Range

0°C To +70°C

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

1016-1287

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XR17C158CV-F

Manufacturer:

Exar Corporation

Quantity:

10 000

Part Number:

XR17C158CV-F

Manufacturer:

EXAR/艾科嘉

Quantity:

20 000

xr

REV. 1.4.3

Interrupt Generation:

• LSR is by any of the LSR bits 1, 2, 3 and 4.

• RXRDY is by RX trigger level.

• RXRDY Time-out is by the a 4-char plus 12 bits delay timer if the RX FIFO level is less than the RX trigger

• TXRDY is by LSR bit-5 (or bit-6 in auto RS485 control).

• MSR is by any of the MSR bits, 0, 1, 2 and 3.

• Receive Xon/Xoff/Special character is by detection of a Xon, Xoff or Special character.

• CTS#/DSR# is by a change of state on the input pin (from LOW to HIGH) with auto flow control enabled,

• RTS#/DTR# is when its receiver changes the state of the output pin (from LOW to HIGH) during auto RTS/

• Wake-up Indicator: when the UART comes out of sleep mode.

Interrupt Clearing:

• LSR interrupt is cleared by a read to the LSR register.

• RXRDY is cleared by reading data until FIFO falls below the trigger level.

• RXRDY Time-out is cleared by reading data until the RX FIFO is empty.

• TXRDY interrupt is cleared by a read to the ISR register.

• MSR interrupt is cleared by a read to the MSR register.

• Xon or Xoff character interrupt is cleared by a read to ISR register.

• Special character interrupt is cleared by a read to ISR register or after the next character is received.

• RTS#/DTR# and CTS#/DSR# status change interrupts are cleared by a read to the MSR register.

• Wake-up Indicator is cleared by a read to the INT0 register.

]

ISR[0]: Interrupt Status

•

•

ISR[3:1]: Interrupt Status

These bits indicate the source for a pending interrupt at interrupt priority levels 1, 2, 3 and 4 (See Interrupt

Source

P

level.

EFR bit-7, and depending on selection of MCR bit-2.

DTR flow control enabled by EFR bit-6 and selection of MCR bit-2.

Logic 0 = An interrupt is pending and the ISR contents may be used as a pointer to the appropriate interrupt

service routine.

Logic 1 = No interrupt pending (default condition).

RIORITY

L

EVEL

1

2

3

4

5

6

7

X

Table

B

IT

0

0

0

0

0

0

1

0

13).

-5

B

IT

0

0

0

0

0

1

0

0

-4

ISR R

B

T

EGISTER

IT

0

0

1

0

0

0

0

0

ABLE

-3

13: I

B

S

IT

TATUS

1

1

1

0

0

0

0

0

-2

NTERRUPT

B

B

ITS

IT

1

0

0

1

0

0

0

0

-1

S

OURCE AND

41

B

IT

0

0

0

0

0

0

0

1

-0

LSR (Receiver Line Status Register)

RXRDY (Received Data Ready)

RXRDY (Receive Data Time-out)

TXRDY (Transmitter Holding Register Empty)

MSR (Modem Status Register)

RXRDY (Received Xon/Xoff or Special character)

CTS#/DSR#, RTS#/DTR# change of state

None (default)

P

RIORITY

L

S

EVEL

OURCE OF THE INTERRUPT

5V PCI BUS OCTAL UART

XR17C158