XR17C158CV-F Exar Corporation, XR17C158CV-F Datasheet - Page 45

XR17C158CV-F

Manufacturer Part Number

XR17C158CV-F

Description

IC UART PCI BUS 5V OCTAL 144LQFP

Manufacturer

Exar Corporation

Type

Universal PCI Bus Octal UARTr

Datasheet

1.XR17C158CV-F.pdf

(67 pages)

Specifications of XR17C158CV-F

Number Of Channels

8

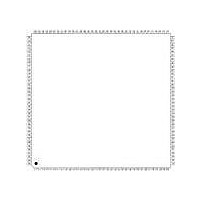

Package / Case

144-LQFP

Features

*

Fifo's

64 Byte

Protocol

RS485

Voltage - Supply

5V

With Auto Flow Control

Yes

With Irda Encoder/decoder

Yes

With False Start Bit Detection

Yes

With Modem Control

Yes

Mounting Type

Surface Mount

Data Rate

6.25 Mbps

Supply Voltage (max)

7 V

Supply Current

5 mA

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Mounting Style

SMD/SMT

Operating Supply Voltage

7 V

No. Of Channels

8

Uart Features

High Performance, Read/Write Burst Operation

Supply Voltage Range

-0.5V To 7V

Operating Temperature Range

0°C To +70°C

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

1016-1287

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XR17C158CV-F

Manufacturer:

Exar Corporation

Quantity:

10 000

Part Number:

XR17C158CV-F

Manufacturer:

EXAR/艾科嘉

Quantity:

20 000

xr

REV. 1.4.3

LCR[6]: Transmit Break Enable

When enabled the Break control bit causes a break condition to be transmitted (the TX output is forced to a

“space", LOW state). This condition remains until disabled by setting LCR bit-6 to a logic 0.

•

•

LCR[7]: Baud Rate Divisors Enable

Baud rate generator divisor (DLL/DLM) enable.

•

•

The MCR register is used for controlling the modem interface signals or general purpose inputs/outputs.

MCR[0]: DTR# Pins

The DTR# pin may be used for automatic hardware flow control enabled by EFR bit-6 and MCR bit-2=1. If the

modem interface is not used, this output may be used for general purpose.

•

•

MCR[1]: RTS# Pins

The RTS# pin may be used for automatic hardware flow control by enabled by EFR bit-6 and MCR bit-2=0. If

the modem interface is not used, this output may be used for general purpose.

•

•

MCR[2]: DTR# or RTS# for Auto Flow Control

DTR# or RTS# auto hardware flow control select. This bit is in effect only when auto RTS/DTR is enabled by

EFR bit-6. DTR# selection is associated with DSR# and RTS# is with CTS#.

•

•

MCR[3]: (OP2)

The OP2 output is not available in the XR17C158. It is present for 16C550 compatibility during internal

loopback. See

MCR[4]: Internal Loopback Enable

•

•

4.8.8

Logic 0 = No TX break condition (default).

Logic 1 = Forces the transmitter output (TX) to a “space”, LOW, for alerting the remote receiver of a line

break condition.

Logic 0 = Data registers are selected (default).

Logic 1 = Divisor latch registers are selected.

Logic 0 = Force DTR# output HIGH (default).

Logic 1 = Force DTR# output LOW.

Logic 0 = Force RTS# output HIGH (default).

Logic 1 = Force RTS# output LOW.

Logic 0 = Uses RTS# and CTS# pins for auto hardware flow control.

Logic 1 = Uses DTR# and DSR# pins for auto hardware flow control.

Logic 0 = Disable internal loopback mode (default).

Logic 1 = Enable internal loopback mode, see loopback section and

Modem Control Register (MCR) - Read/Write

Figure

16. Logic 0 is default.

LCR B

X

0

0

1

1

IT

-5 LCR B

X

0

1

0

1

T

ABLE

IT

-4 LCR B

15: P

0

1

1

1

1

ARITY SELECTION

IT

45

-3

Forced parity to space, “0”

Force parity to mark, “1”

P

ARITY SELECTION

Even parity

Odd parity

No parity

Figure

16.

5V PCI BUS OCTAL UART

XR17C158