EPM240GM100C5N Altera, EPM240GM100C5N Datasheet - Page 18

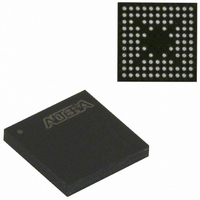

EPM240GM100C5N

Manufacturer Part Number

EPM240GM100C5N

Description

IC MAX II CPLD 240 LE 100-MBGA

Manufacturer

Altera

Series

MAX® IIr

Datasheets

1.EPM240GT100C5N.pdf

(6 pages)

2.EPM240GT100C5N.pdf

(88 pages)

3.EPM240GM100C5N.pdf

(10 pages)

Specifications of EPM240GM100C5N

Programmable Type

In System Programmable

Delay Time Tpd(1) Max

4.7ns

Voltage Supply - Internal

1.71 V ~ 1.89 V

Number Of Logic Elements/blocks

240

Number Of Macrocells

192

Number Of I /o

80

Operating Temperature

0°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

100-MBGA

Voltage

1.8V

Memory Type

FLASH

Number Of Logic Elements/cells

240

Family Name

MAX II

# Macrocells

192

Frequency (max)

1.8797GHz

Propagation Delay Time

7.5ns

Number Of Logic Blocks/elements

24

# I/os (max)

80

Operating Supply Voltage (typ)

1.8V

In System Programmable

Yes

Operating Supply Voltage (min)

1.71V

Operating Supply Voltage (max)

1.89V

Operating Temp Range

0C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

100

Package Type

MBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Compliant

Other names

544-1726

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EPM240GM100C5N

Manufacturer:

CYPESS

Quantity:

1

Company:

Part Number:

EPM240GM100C5N

Manufacturer:

ALTERA10

Quantity:

1 287

Part Number:

EPM240GM100C5N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

2–10

Figure 2–8. LE in Dynamic Arithmetic Mode

Note to

(1) The addnsub signal is tied to the carry input for the first LE of a carry chain only.

MAX II Device Handbook

LAB Carry-In

Carry-In0

Carry-In1

Figure

data1

data2

data3

(LAB Wide)

addnsub

2–8:

(1)

The other two LUTs use the data1 and data2 signals to generate two possible carry-out

signals: one for a carry of 1 and the other for a carry of 0. The carry-in0 signal acts

as the carry-select for the carry-out0 output and carry-in1 acts as the carry-

select for the carry-out1 output. LEs in arithmetic mode can drive out registered

and unregistered versions of the LUT output.

The dynamic arithmetic mode also offers clock enable, counter enable, synchronous

up/down control, synchronous clear, synchronous load, and dynamic

adder/subtractor options. The LAB local interconnect data inputs generate the

counter enable and synchronous up/down control signals. The synchronous clear

and synchronous load options are LAB-wide signals that affect all registers in the

LAB. The Quartus II software automatically places any registers that are not used by

the counter into other LABs. The addnsub LAB-wide signal controls whether the LE

acts as an adder or subtractor.

Carry-Select Chain

The carry-select chain provides a very fast carry-select function between LEs in

dynamic arithmetic mode. The carry-select chain uses the redundant carry calculation

to increase the speed of carry functions. The LE is configured to calculate outputs for a

possible carry-in of 0 and carry-in of 1 in parallel. The carry-in0 and carry-in1

signals from a lower-order bit feed forward into the higher-order bit via the parallel

carry chain and feed into both the LUT and the next portion of the carry chain. Carry-

select chains can begin in any LE within an LAB.

Carry-Out0

LUT

LUT

LUT

LUT

Carry-Out1

Register chain

connection

clock (LAB Wide)

(LAB Wide)

ena (LAB Wide)

aclr (LAB Wide)

sload

(LAB Wide)

sclear

Register Feedback

(LAB Wide)

ADATA

ENA

D

ALD/PRE

aload

CLRN

Q

© October 2008 Altera Corporation

Chapter 2: MAX II Architecture

Row, column, and

direct link routing

Row, column, and

direct link routing

Local routing

LUT chain

connection

Register

chain output

Logic Elements