EP3C55F484I7 Altera, EP3C55F484I7 Datasheet - Page 58

EP3C55F484I7

Manufacturer Part Number

EP3C55F484I7

Description

IC CYCLONE III FPGA 55K 484 FBGA

Manufacturer

Altera

Series

Cyclone® IIIr

Datasheets

1.EP3C5F256C8N.pdf

(5 pages)

2.EP3C5F256C8N.pdf

(34 pages)

3.EP3C5F256C8N.pdf

(66 pages)

4.EP3C5F256C8N.pdf

(14 pages)

5.EP3C5F256C8N.pdf

(76 pages)

Specifications of EP3C55F484I7

Number Of Logic Elements/cells

55856

Number Of Labs/clbs

3491

Total Ram Bits

2396160

Number Of I /o

327

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

-40°C ~ 100°C

Package / Case

484-FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP3C55F484I7

Manufacturer:

TI

Quantity:

2 847

Company:

Part Number:

EP3C55F484I7N

Manufacturer:

FREESCALE

Quantity:

1 445

Company:

Part Number:

EP3C55F484I7N

Manufacturer:

ALTERA

Quantity:

118

Part Number:

EP3C55F484I7N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

2–14

Switching Characteristics

Core Performance Specifications

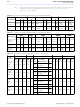

Table 2–20. Cyclone III LS Devices PLL Specifications

Cyclone III Device Handbook, Volume 2

f

f

f

f

t

IN

INPF D

VC O

INDUTY

INJITTER_C CJ

(1)

(6)

(5)

Symbol

f

For more information about power estimation tools, refer to the

User Guide

Handbook.

This section describes performance characteristics of the core and periphery blocks for

Cyclone III LS devices. These characteristics are designated as Preliminary or Final,

as indicated in the title of each table. The designations are defined as follows:

■

■

Table 2–19

Cyclone III LS devices.

Clock Tree Specifications

Table 2–19

Table 2–19. Cyclone III LS Devices Clock Tree Performance (Preliminary)

PLL Specifications

Table 2–20

the commercial junction temperature range (0°C to 85°C) and the industrial junction

temperature range (-40°C to 100°C). For more information about the PLL block, refer

to

EP3CLS70

EP3CLS100

EP3CLS150

EP3CLS200

“PLL Block”

Preliminary—Preliminary characteristics are created using simulation results,

process data, and other known parameters.

Final—Final numbers are based on actual silicon characterization and testing.

These numbers reflect the actual performance of the device under worst-case

silicon process, voltage, and junction temperature conditions.

Device

Input clock frequency

PFD input frequency

PLL internal VCO operating range

Input clock duty cycle

Input clock cycle-to-cycle jitter F

F

REF

< 100 MHz

through

lists the clock tree specifications for Cyclone III LS devices.

lists the PLL specifications for Cyclone III LS devices when operating in

and the

in

“Glossary” on page

PowerPlay Power Analysis

Table 2–25

437.5

437.5

437.5

437.5

Parameter

C7

(Note 4)

describe the core performance specifications for

REF

≥ 100 MHz

(Part 1 of 2) (Preliminary)

Performance

2–26.

402

402

402

402

C8

chapter in volume 3 of the Quartus II

Chapter 2: Cyclone III LS Device Data Sheet

Min

600

—

40

—

—

5

437.5

437.5

437.5

437.5

© December 2009 Altera Corporation

I7

Typ

—

—

—

—

—

—

Early Power Estimator

Switching Characteristics

1300

±750

0.15

Max

450

325

60

MHz

MHz

MHz

MHz

Unit

MHz

MHz

MHz

Unit

UI

ps

%