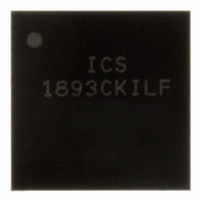

ICS1893CKILF IDT, Integrated Device Technology Inc, ICS1893CKILF Datasheet - Page 18

ICS1893CKILF

Manufacturer Part Number

ICS1893CKILF

Description

PHYCEIVER LOW PWR 3.3V 56-MLF2

Manufacturer

IDT, Integrated Device Technology Inc

Series

PHYceiver™r

Type

PHY Transceiverr

Datasheet

1.ICS1893CFLFT.pdf

(127 pages)

Specifications of ICS1893CKILF

Protocol

MII

Voltage - Supply

3.14 V ~ 3.47 V

Mounting Type

Surface Mount

Package / Case

56-VQFN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Drivers/receivers

-

Lead Free Status / RoHS Status

Compliant, Lead free / RoHS Compliant

Other names

1893CKILF

800-1023

800-1023

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ICS1893CKILF

Manufacturer:

IDT

Quantity:

206

Company:

Part Number:

ICS1893CKILFT

Manufacturer:

ST

Quantity:

785

Part Number:

ICS1893CKILFT

Manufacturer:

ICS

Quantity:

20 000

5.2 Serial Management Interface

5.3 Twisted-Pair Interface

5.3.1 Twisted-Pair Transmitter

ICS1893CF, Rev. K, 05/13/10

The ICS1893CF provides an ISO/IEC compliant, two-wire Serial Management Interface as part of its MAC

Interface. This Serial Management Interface is used to exchange control, status, and configuration

information between a Station Management entity (STA) and the physical layer device (PHY), that is, the

ICS1893CF.

The ISO/IEC standard also specifies a frame structure and protocol for this interface as well as a set of

Management Registers that provide the STA with access to a PHY such as the ICS1893CF. A Serial

Management Interface is comprised of two signals: a bi-directional data pin (MDIO) along with an

associated input pin for a clock (MDC). The clock is used to synchronize all data transfers between the

ICS1893CF and the STA.

In addition to the ISO/IEC defined registers, the ICS1893CF provides several extended status and control

registers to provide more refined control of the MII and MDI interfaces. For example, the QuickPoll Detailed

Status Register provides the ability to acquire the most-important status functions with a single MDIO read.

Note:

For the twisted-pair interface, the ICS1893CF uses 1:1 ratio transformers for both transmit and receive.

Better operation results from using a split ground plane through the transformer. In this case:

•

•

•

The twisted-pair transmitter driver uses an H-bridge configuration. IDT transformer requirements:

•

•

•

•

Figure 5-1

•

•

Note:

1. Keep all TX traces as short as possible.

2. When longer board twisted pair traces are used, 50Ω-characteristic board trace impedance is

The RJ-45 transformer windings must be on the chassis ground plane along with the Bob Smith

termination.

The ICS1893CF system ground plane must include the ICS1893CF-side transformer windings along

with the 49.9Ω resistors and the 100 nF capacitor.

The transformer provides the isolation with one set of windings on one ground plane and another set of

windings on the second ground plane.

Turns Ratio 1:1

Chokes may be used on chip or cable side or both sides

No power connections to the transformer. Transformer power is supplied by the ICS1893CF

MIDCOM 7090-37 or equivalent symetrical magnetics are used

Two 49.9Ω 1% resistors are in series with a 100 nF capacitor to ground between them. These

components form a network that connects across both pairs of twisted pairs A and B.

Both twisted pairs A and B have an assigned plus and minus.

desirable.

In the ICS1893CF, the MDIO and MDC pins remain active for all the MAC Interface modes (that is,

10M MII, 100M MII, 100M Symbol, and 10M Serial).

ICS1893CF Data Sheet - Release

shows the design for the ICS1893CF twisted-pair interface.

Copyright © 2009, Integrated Device Technology, Inc.

All rights reserved.

18

Chapter 5 Interface Overviews

May, 2010