DS26519GN+ Maxim Integrated Products, DS26519GN+ Datasheet - Page 24

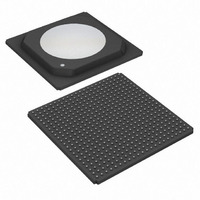

DS26519GN+

Manufacturer Part Number

DS26519GN+

Description

IC TXRX T1/E1/J1 16PRT 484-HSBGA

Manufacturer

Maxim Integrated Products

Type

Transceiverr

Datasheet

1.DS26519GN.pdf

(310 pages)

Specifications of DS26519GN+

Number Of Drivers/receivers

16/16

Protocol

Ethernet

Voltage - Supply

3.135 V ~ 3.465 V

Mounting Type

Surface Mount

Package / Case

484-BGA Exposed Pad, 484-eBGA, 484-HBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 24 of 310

- Download datasheet (9Mb)

TCHBLK10/

TCHBLK11/

TCHBLK12/

TCHBLK13/

TCHBLK14/

TCHBLK15/

TCHBLK16/

TCHCLK10

TCHCLK11

TCHCLK12

TCHCLK13

TCHCLK14

TCHCLK15

TCHCLK16

TCHBLK1/

TCHBLK2/

TCHBLK3/

TCHBLK4/

TCHBLK5/

TCHBLK6/

TCHBLK7/

TCHBLK8/

TCHBLK9/

TCHCLK1

TCHCLK2

TCHCLK3

TCHCLK4

TCHCLK5

TCHCLK6

TCHCLK7

TCHCLK8

TCHCLK9

NAME

W10

W22

A15

A17

E14

H12

N20

Y22

PIN

F16

N9

D1

G2

V8

V9

Y5

K6

Output

TYPE

Transmit Channel Block/Transmit Channel Block Clock. A dual function pin.

TCHBLK[1:16]. TCHBLKn is a user-programmable output that can be forced

high or low during any of the channels. It is synchronous with TCLKn when the

transmit-side elastic store is disabled. It is synchronous with TSYSCLKn when

the transmit-side elastic store is enabled. It is useful for blocking clocks to a serial

UART or LAPD controller in applications where not all channels are used such as

Fractional T1, Fractional E1, 384kbps (H0), 768kbps, or ISDN-PRI. Also useful

for locating individual channels in drop-and-insert applications, for external per-

channel loopback, and for per-channel conditioning.

TCHCLK[1:16]. TCHCLKn is a dual function pin that can output either a gapped

clock or a channel clock. In gapped clock mode, TCHCLKn is a N x 64kHz

fractional clock, which is software programmable for 0 to 24 channels and the

F-bit (T1) or 0 to 32 channels (E1). In channel clock mode, TCHCLKn is a

192kHz (T1) or 256kHz (E1) clock that pulses high during the LSB of each

channel. It is useful for parallel-to-serial conversion of channel data. In either

mode, TCHCLKn is synchronous with TCLKn when the receive-side elastic store

is disabled or it is synchronous with TSYSCLKn when the receive-side elastic

store is enabled. The mode of TCHCLK is determined by the TGCLKEN bit in the

TESCR register.

24 of 310

FUNCTION

DS26519 16-Port T1/E1/J1 Transceiver

Related parts for DS26519GN+

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Ds26519 16-port T1/e1/j1 Transceiver

Manufacturer:

Maxim Integrated Products, Inc.

Datasheet:

Part Number:

Description:

power light source LUXEON® Collimator

Manufacturer:

LUMILEDS [Lumileds Lighting Company]

Datasheet:

Part Number:

Description:

MAX7528KCWPMaxim Integrated Products [CMOS Dual 8-Bit Buffered Multiplying DACs]

Manufacturer:

Maxim Integrated Products

Datasheet:

Part Number:

Description:

Single +5V, fully integrated, 1.25Gbps laser diode driver.

Manufacturer:

Maxim Integrated Products

Datasheet:

Part Number:

Description:

Single +5V, fully integrated, 155Mbps laser diode driver.

Manufacturer:

Maxim Integrated Products

Datasheet:

Part Number:

Description:

VRD11/VRD10, K8 Rev F 2/3/4-Phase PWM Controllers with Integrated Dual MOSFET Drivers

Manufacturer:

Maxim Integrated Products

Datasheet:

Part Number:

Description:

Highly Integrated Level 2 SMBus Battery Chargers

Manufacturer:

Maxim Integrated Products

Datasheet:

Part Number:

Description:

Current Monitor and Accumulator with Integrated Sense Resistor; ; Temperature Range: -40°C to +85°C

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

TSSOP 14/A°/RS-485 Transceivers with Integrated 100O/120O Termination Resis

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

TSSOP 14/A°/RS-485 Transceivers with Integrated 100O/120O Termination Resis

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

QFN 16/A°/AC-DC and DC-DC Peak-Current-Mode Converters with Integrated Step

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

TDFN/A/65V, 1A, 600KHZ, SYNCHRONOUS STEP-DOWN REGULATOR WITH INTEGRATED SWI

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Integrated Temperature Controller f

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

SOT23-6/I°/45MHz to 650MHz, Integrated IF VCOs with Differential Output

Manufacturer:

Maxim Integrated Products