tda8757a NXP Semiconductors, tda8757a Datasheet

tda8757a

Related parts for tda8757a

tda8757a Summary of contents

Page 1

... Triple 8-bit ADC 205 Msps Rev. 01 — 22 March 2002 1. General description The TDA8757A is a triple 8-bit ADC for the digitizing of large bandwidth RGB/YUV signals at a sampling rate up to 205 Msps. The IC supports display resolutions up to 1600 The IC also includes a PLL that can be locked to the horizontal line frequency and generates the ADC clock ...

Page 2

... MHz clk V = 2.5 V with ref 100 ppm/ C maximum 3 dB amb input signal settling time <1 ns; settling to 1 MHz i Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps Min Typ Max Unit 4.75 5.0 5.25 V 4.75 5.0 5.25 V 4.75 5.0 5. ...

Page 3

... Preliminary data Conditions Min 100 f = 205 MHz; sine wave clk input f = 205 MHz clk 20 1.4 mm; exposed die pad Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps Typ Max Unit 4095 1.7 W 336 ps Sampling frequency Version (MHz) SOT612-1 170 205 © ...

Page 4

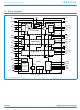

... REGULATOR 2 I C-bus 132 4 2 130 141 HSYNC DEC1 DEC2 PD CZ Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps CLP R 6 BOT R 8 114 to 121 100 to 107 OUTPUT 113 OR R 129 OE 18 ...

Page 5

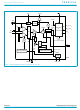

... ADC C-bus bits REGISTER COARSE GAIN ADJUST (F ) GAINC HSYNC stands for B). Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps OE CKDMX C-bus bits 8 OUTPUTS & OUTPUTS ...

Page 6

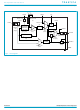

... VCO PHASE 2 I C-bus C-bus: 2 bits 1 bit (Vco) (Ckext) (Di) SYNCHRO MUX 2 I C-bus: 1 bit (Ckrs) Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps INV CKADC 0/180 CKDMX 2 I C-bus: 1 bit (Odda) / MUX 2 I C-bus: 2 bits 2 (Ckdd, Ckdp C-bus: ...

Page 7

... TDA8757AHL Pin description Pin Description 1 not connected 2 main regulator decoupling input 2 3 gain stabilizer voltage reference input 4 main regulator decoupling input 1 Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps n.c. 108 107 B7 R 106 B6 R 105 B5 R 104 B4 R 103 ...

Page 8

... I C-bus and 3W-bus disable control input (disable at HIGH level) 43 select enable input for 3W-bus Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps 2 C-bus (active HIGH) and 3W-bus © Koninklijke Philips Electronics N.V. 2002. All rights reserved ...

Page 9

... ADC output B bit 2 82 green channel ADC output B bit 3 83 green channel ADC output B bit 4 84 green channel ADC output B bit 5 Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps © Koninklijke Philips Electronics N.V. 2002. All rights reserved ...

Page 10

... ADC output A bit 7 (MSB) 122 PLL digital ground PLL 123 output data clock 124 output horizontal pulse synchronized to pixel clock 125 output reserved for test Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps © Koninklijke Philips Electronics N.V. 2002. All rights reserved ...

Page 11

... Figure 5). The maximum amplitude for the sync pulse is 600 mV typical. Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps (AC coupled). When SOG 2 C-bus bit ‘Slevel’ has to be set to (TTL level compatible signal). ...

Page 12

... LOW-level TTL. O Table 5). Each clamp must be able to correct an , CLP R video signal Clamp = 128 Clamp = 64 Clamp = 0 Clamp = 63.5 Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps 2 C-bus bit Slevel = 0 2 C-bus bit Slevel = 1 005aaa009 1 LSB (YUV). 2 and CLP . G B 255 constant level ...

Page 13

... V (DC), with a maximum variation of 100 ppm ref The ADCs inputs become this reference 16 ref Table 6). 1 LSB peak-to-peak (see Equation 2 Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps Thus, three 16 ref 3). © Koninklijke Philips Electronics N.V. 2002. All rights reserved ...

Page 14

... This mode is activated through the serial interface by setting bit ‘Blk’ to logic 1 in register DEMUX. The TDA8757A provides outputs either on one port (port two ports (ports A and B). The selection is made with the serial interface by setting bit ‘Dmx’ to logic 0 or logic 1 in register DEMUX ...

Page 15

... PLL loop filter. The recommended and C = 150 pF Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps Table must be chosen so that: cp give the same result, a calculating cp © Koninklijke Philips Electronics N.V. 2002. All rights reserved. ...

Page 16

... CKAO = CLK(buffer) phase selector phase = tbf and t = --------------- phase selector 2 Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps ns, compared to t CKAO t CKREFO FCE699 : CKREFO + T (if phase <01000) CKAO CLK(pixel) T CLK pixel © Koninklijke Philips Electronics N.V. 2002. All rights reserved. ...

Page 17

... All the registers are programmed one after the other, by giving this initial condition (XXX1 1111) as the subaddress state; thus, the registers are changed following the predefined sequence of 16 bytes (from subaddress 0000 to 1101). Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps Table 4. Default ...

Page 18

... V FINE V 1 – ----------------- - ref 2.5 V. ref Table = 0). FINE Typical gain correspondence (COARSE) Gain 0.825 2 Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps ADC output underflow 0 ... 120 ... 136 COARSE 32 . 512 N – ref FINE 6. The gain is linear with reference to the ...

Page 19

... FINE Table 8. Charge pump current control Ip1 Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps 1 LSB peak-to-peak (see full-scale (V) i 1.212 1.139 2 C-bus control bits ‘Vlevel’ Ip0 Current ( ...

Page 20

... Preliminary data VCO register bits Vco0 C-bus programming is done in mode 1 and the bit ‘Di0’ has to be Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps Z0 Resistance ( high-impedance 6.4 1 4.5 0 3.2 1 2.25 0 1.6 1 1.1 ...

Page 21

... C-bus is 1001 1XX0. 2 C-bus are standard. Two sequences are available; and 14. Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps P0 Phase shift (deg 11.25 ... ... 0 337.5 1 348.75 Figure © ...

Page 22

... h3W = 100 ns Parameter Conditions analog supply voltage logic supply voltage digital supply voltage output stages supply voltage Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps SUBADDRESS A ... P REGISTER2 DATA A ... P REGISTER2 Table 4) ...

Page 23

... Parameter thermal resistance from junction to ambient = 4. 5.25 V (referenced to DGND); V CCD = and T CCA DDD CCD CCO Conditions 2 C-bus Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps Min Max Unit 1.0 +1.0 V 1.0 +1.0 V 1.0 +1.0 V 1.0 +1.0 V 1.0 +1.0 V 1.0 +1 ...

Page 24

... V with 100 ppm/ C ref maximum variation HSYNC active; capacitors on pins 8, 16 and 24 are 22 nF Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps = 4. 5.25 V DDD connected together unless otherwise amb Min Typ Max ...

Page 25

... IC analog input to digital output; sine wave input 205 MHz clk from IC analog input to digital output; sine wave input 205 MHz clk Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps = 4. 5.25 V DDD connected together unless otherwise amb Min Typ Max Unit 0 ...

Page 26

... Conditions f = 205 MHz clk f = 205 MHz clk referenced to CKDATA C/3W, OE, CKEXT) 2 C/3W, OE)) Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps = 4. 5.25 V DDD connected together unless otherwise amb Min Typ Max Unit ...

Page 27

... V PU for SCL and SDA repeated start f = 100 kHz SCL f = 100 kHz SCL 6.02 + 1.76 dB. Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps = 4. 5.25 V DDD connected together and unless otherwise amb Min Typ Max 300 600 150 ...

Page 28

... CPH t CPL n t su(d)( d(s) Sample n 2 Sample n 1 Sample Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps I Z Long-term time jitter RMS-value peak-to-peak (ps) value (ps) 700 1.6 tbf tbf 400 3.2 tbf tbf ...

Page 29

... Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps MGW782 MGW785 MGW781 ...

Page 30

... Preliminary data Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps MGW784 MGW783 © Koninklijke Philips Electronics N.V. 2002. All rights reserved. ...

Page 31

... IN B BIN 32 AGND n.c. 35 n.c. 36 For interfacing the 5 V digital outputs of the TDA8757A to devices with 3 V compliant inputs, a resistor bridge (220 820 to ground) should be applied to each digital output. Fig 18. Application diagram. 9397 750 09549 Preliminary data 150 pF TDA8757AHL ...

Page 32

... scale (1) ( 20.1 7.1 20.1 7.1 22.15 22.15 0.5 19.9 6.9 19.9 6.9 21.85 21.85 REFERENCES JEDEC JEITA MS-026 Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps SOT612 detail X (1) ( 0.75 1.4 1.4 1 0.2 0.08 0.08 0.45 1.1 1.1 EUROPEAN ISSUE DATE ...

Page 33

... Preliminary data Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps © Koninklijke Philips Electronics N.V. 2002. All rights reserved ...

Page 34

... Wave soldering is only suitable for SSOP and TSSOP packages with a pitch (e) equal to or larger than 0.65 mm definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5 mm. 9397 750 09549 Preliminary data methods [3] , SO, SOJ Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps Soldering method Wave Reflow not suitable suitable [2] ...

Page 35

... Philips Semiconductors 17. Revision history Table 20: Revision history Rev Date CPCN Description 01 20020322 - Preliminary specification; initial version. 9397 750 09549 Preliminary data Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps © Koninklijke Philips Electronics N.V. 2002. All rights reserved ...

Page 36

... Licenses Purchase of Philips I Rev. 01 — 22 March 2002 TDA8757A Triple 8-bit ADC 205 Msps performance. Philips Semiconductors 2 C components ...

Page 37

... Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights. Date of release: 22 March 2002 Document order number: 9397 750 09549 TDA8757A Triple 8-bit ADC 205 Msps 20 Disclaimers . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 21 ...