saa6712e NXP Semiconductors, saa6712e Datasheet

saa6712e

Related parts for saa6712e

saa6712e Summary of contents

Page 1

... DATA SHEET SAA6712E XGA RGB to TFT graphics engine Preliminary specification File under Integrated Circuits, IC02 INTEGRATED CIRCUITS 1999 Aug 25 ...

Page 2

... TIMING CHARACTERISTICS 12 APPLICATION INFORMATION 13 PACKAGE OUTLINE 14 SOLDERING 14.1 Introduction to soldering surface mount packages 14.2 Reflow soldering 14.3 Wave soldering 14.4 Manual soldering 14.5 Suitability of surface mount IC packages for wave and reflow soldering methods 15 DEFINITIONS 16 LIFE SUPPORT APPLICATIONS 17 PURCHASE OF PHILIPS I 2 Preliminary specification SAA6712E 2 C COMPONENTS ...

Page 3

... Internal Phase-Locked Loop (PLL) for memory and panel clock generation from the system clock 2 I C-bus interface with 2 selectable addresses Boundary scan test circuit and Joint Test Action Group (JTAG) test controller Pin compatible to SAA6721E Programming compatible to SAA6721E. 3 Preliminary specification SAA6712E 16 SDRAM, 256k 32 SGRAM or ...

Page 4

... TYPE NUMBER NAME SAA6712E BGA292 1999 Aug 25 The SAA6712E must be embedded into a system containing a microcontroller with an I interface. For auto-scan capabilities a frame buffer built from SGRAM or SDRAM is needed. The size of this frame buffer depends on the maximum resolution and bandwidth needed for the application. For converting the analog RGB stream into a digital data stream one or two ADCs with 3 channels each for R, G and B are needed ...

Page 5

... GLOBAL CONTROL JTAG UNIT CONTROLLER LINE MEMORY UP- COLOUR PANNING SCALER CORRECTION UNIT SDRAM MEMORY INTERFACE ON TEMPORAL SCREEN DITHERING DISPLAY SAA6712E BA RAS WE A10 to A0 DQM CAS MCLKO Fig.1 Block diagram. OVA2 to OVA0 OVVS OVB2 OVHS TCLK to OVCLK OVACT OVB0 OSD ...

Page 6

... Fig.2 Pin configuration (bottom view). (1) I/O input RGB sample clock input RGB vertical sync input RGB horizontal sync input video input port A; RGB port 0 red channel input input input input input input input 6 Preliminary specification SAA6712E MHB458 DESCRIPTION ...

Page 7

... E; RGB port 1 green channel input input input input input input input input video input port F; RGB port 1 blue channel input input input input input input input 7 Preliminary specification SAA6712E DESCRIPTION ...

Page 8

... A green channel output output output output output output output output panel port A blue channel output output output output output output output output panel port B red channel output output output output output output output 8 Preliminary specification SAA6712E DESCRIPTION ...

Page 9

... Row Address Strobe (RAS) signal (active LOW) output memory Column Address Strobe (CAS) signal (active LOW) output memory Write Enable (WE) signal (active LOW) output memory data mask (active LOW) 9 Preliminary specification SAA6712E DESCRIPTION ...

Page 10

... Preliminary specification SAA6712E DESCRIPTION ...

Page 11

... JTAG test controller clock; note 2 input JTAG test controller reset (active LOW); note 2 input JTAG test data input; note 2 input JTAG test mode select; note 2 output JTAG test data output 11 Preliminary specification SAA6712E DESCRIPTION ...

Page 12

... PLL circuitry supply voltage for internal PLL circuitry not connected not connected not connected not connected not connected not connected not connected not connected not connected not connected 12 Preliminary specification SAA6712E DESCRIPTION ...

Page 13

... It can be generated internally by the PLL from the system clock (CLK external quartz oscillator. If the internal PLL is used, the memory clock frequency can be derived from the following formula: f_system f_memory = ----------------------- - N Where N = pre-divider ratio and f_system = clock at pin CLK. 13 Preliminary specification SAA6712E (VCLK) (MCLKI) 16 ...

Page 14

... VVS, and the horizontal synchronization pulse is connected to pin VHS. For calibrating the connected Analog-to-Digital Converter (ADC) the SAA6712E delivers a clamp pulse at pin CLAMP, and a gain correction pulse at pin GAINC (see Fig.4). The sample window of the RGB input port is controlled by four counters ...

Page 15

... Mbytes. But only half of this memory will be used by the SAA6712E. The memory port of the SAA6712E can be divided into 4 SDRAM channels. Each channel is 16 bits wide, and provides in High Speed Channel (HSC) mode with a 125 MHz memory clock and an effective bandwidth of 228 Mbits/s ...

Page 16

... With these devices a frame buffer can be built, without wasting memory because of bandwidth. In case of SGRAM usage, the memory data bus of the SAA6712E can be split into 2 channels of 32 bits each. Table 3 SGRAM channel configurations ...

Page 17

... If write mode was selected, the master sends the register address to be written and then the data bytes. If read mode was selected, the SAA6712E sends the data bytes starting from the last address accessed either by write command or the next address at a read command. ...

Page 18

... Philips Semiconductors XGA RGB to TFT graphics engine 7.7 Scaling algorithm The SAA6712E features different scaling engines for up and downscaling, for both horizontal and vertical processing. The horizontal scaling engines are independent from each other. The vertical scaling engines share the line buffer, so they cannot operate in parallel. ...

Page 19

... XGA RGB to TFT graphics engine 8 SYSTEM DESCRIPTION 8.1 Programming registers The SAA6712E is a highly integrated device with many features. To get the desired functionality and performance it must be programmed correctly. In general, before programming, the device must be switched to the internal reset state to prevent unwanted functions while changing the registers ...

Page 20

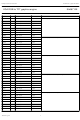

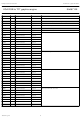

... Preliminary specification SAA6712E non_black_pixels[ memory_ reset_ reset_ init input_path memory_ path frc_on blank_ screen post_div_ pll_enable pll_pclk half_clock pre_div_clock_p_low pre_div_clock_n_low ...

Page 21

... Preliminary specification SAA6712E data_width[1 and 0] burst_seq_length SDRAM_burst_length t_RCD t_RP t_RC field_row[ frame_length[ line_length[ up_v_ ...

Page 22

... W ovl_colour2_blue 1999 Aug coeff_index coeff_value ovl_act_ ovl_vs_ ovl_hs_ pol pol pol 22 Preliminary specification SAA6712E pic_v_offset[ pic_h_offset[ out_v_size[ out_h_size[ clk_ sample_ ovl_ gating_on edge syncs_ active ovl_hs_start[ ovl_hs_length[ ...

Page 23

... W osd_fg_colour3_blue 156 W osd_fg_colour4_red 157 W osd_fg_colour4_green 158 W osd_fg_colour4_blue 159 W osd_fg_colour5_red 160 W osd_fg_colour5_green 1999 Aug osd_v_size osd_h_size Preliminary specification SAA6712E zoom2 char_size osd_v_offset[ osd_h_offset[ osd_ active ...

Page 24

... Preliminary specification SAA6712E osd_fg_ osd_fg_ osd_fg_ colour3_ colour2_ colour1_ transp transp transp osd_fg_ osd_fg_ osd_fg_ colour3_ colour2_ colour1_ alpha alpha ...

Page 25

... Preliminary specification SAA6712E osd_bg_ osd_bg_ osd_bg_ colour3_ colour2_ colour1_ alpha alpha alpha char_fg_colour hsync_pol de_pol clk_pol sync_ blank_ctrl ...

Page 26

... Negative Vsync Positive Vsync V ERTICAL FRAME RESOLUTION Number of lines between two Vsyncs H ORIZONTAL FRAME RESOLUTION Number of clocks between two Hsyncs 1999 Aug Preliminary specification SAA6712E h_de_end[ h_active_start[ v_vs_end[ h_max_len[ SUBADDRESS R ...

Page 27

... Aug 25 SUBADDRESS R/W 9 and and and 19 20 and 21 22 and 23 27 Preliminary specification SAA6712E DATA D10 to D0 D11 D10 D11 to D0 ...

Page 28

... Normal data processing Blank screen generation after memory interface Output temporal dithering No temporal dithering of output data stream Temporal dithering of output data 1999 Aug 25 SUBADDRESS R Preliminary specification SAA6712E DATA D0 logic 0 logic 1 D1 logic 0 logic 1 D2 logic 0 logic 1 D3 logic 0 logic 1 ...

Page 29

... DIVIDER N OFFSET Post-divider n-counter offset programming 1999 Aug 25 SUBADDRESS R Preliminary specification SAA6712E DATA D0 logic 0 logic 1 D1 logic 0 logic 1 D2 logic 0 logic 1 D3 logic 0 logic 1 D4 logic 0 logic 1 D5 logic 0 logic 1 D6 logic 0 logic 1 ...

Page 30

... SUBADDRESS R and and and and Preliminary specification SAA6712E DATA D0 logic 0 logic 1 D1 logic 0 logic 1 D2 logic 0 logic 1 D3 logic 0 logic 1 D4 logic 0 logic 1 D6 logic 0 logic 1 D10 to D0 D11 to D0 D10 to D0 ...

Page 31

... TIMING PARAMETER SEE Precharge command period (t RP Active bank A to active band B command (t 1999 Aug ABLE ) in clocks T 10 ABLE ) in clocks ) in clocks RRD 31 Preliminary specification SAA6712E SUBADDRESS R logic 0 logic 1 D1 logic 0 logic 1 D2 logic 0 logic 1 D3 logic 0 logic 1 48 ...

Page 32

... LANK COLOUR GREEN COMPONENT DEFINITION Green colour component for blank screen generation B LANK COLOUR BLUE COMPONENT DEFINITION Blue colour component for blank screen generation 1999 Aug ABLE ) in clocks RC 32 Preliminary specification SAA6712E SUBADDRESS R and 57 W D10 ...

Page 33

... Fraction of vertical downscaling increment ( H ORIZONTAL DOWNSCALE INCREMENT Increment for horizontal downscaling 1999 Aug 25 SUBADDRESS 76 and 100 79 and 100 1 ) 100 33 Preliminary specification SAA6712E R/W DATA logic 0 logic 1 D1 logic 0 logic 1 D2 logic 0 logic 1 D3 logic 0 logic 1 D4 logic 0 logic 1 ...

Page 34

... Blue colour component for border generation 1999 Aug 25 SUBADDRESS 100 and 89 90 and 91 92 and 93 94 and Preliminary specification SAA6712E R/W DATA D10 D11 D10 D11 ...

Page 35

... Aug 25 SUBADDRESS R 100 and 101 W 102 and 103 W 104 W 105 and 106 W 107 and 108 W 109 and 110 W 35 Preliminary specification SAA6712E DATA D0 logic 0 logic 1 D1 logic 0 logic 1 D2 logic 0 logic 1 D3 logic 0 logic 1 D4 logic 0 logic 1 D5 logic 0 ...

Page 36

... W 138 and 139 W 140 and 141 W 142 W 143 W 144, 147, 150, W 153, 156, 159, 162 and 165 36 Preliminary specification SAA6712E DATA D10 logic 0 logic 1 D1 logic 0 logic 1 D2 logic 0 logic 1 D10 to D0 D11 to D0 ...

Page 37

... W 179, 182, 185, 188 and 191 192 W 193 W 194 W 195 W 37 Preliminary specification SAA6712E DATA logic 0 logic logic 0 logic logic 0 logic 1 ...

Page 38

... SUBADDRESS R/W 196 W 197 W 198 W 199 W 200 W 201 W 202 W 38 Preliminary specification SAA6712E DATA and and and and and logic 0 logic 1 D1 ...

Page 39

... W 206 and 207 W 208 and 209 W 210 and 211 W 212 and 213 W 214 and 215 W 216 and 217 W 39 Preliminary specification SAA6712E DATA D0 logic 0 logic 1 D1 logic 0 logic 1 D2 logic 0 logic 1 D3 logic 0 logic 1 D4 logic 0 logic 1 ...

Page 40

... Clock management 8.2.1 C LOCK GENERATION AND MULTIPLEXING For normal operation the SAA6712E uses two clock inputs; pin VCLK and pin CLK. VCLK is used as the sample clock provided by the external ADCs or decoder. The frequency and the sample edges of this clock depend on the number of ADCs connected the video dot ...

Page 41

... Table 7 Clock divider programming P-COUNTER RATIO 1.5 2.0 2.5 3.0 3.5 1999 Aug 25 PRE-DIVIDER PLL 32 Fig.8 Clock generator. Fig.9 Clock waveforms. N-COUNTER (HEX) (HEX Preliminary specification SAA6712E MCLKO 2 POST-DIVIDER PCLK MHB251 N-OFFSET HALF CLK COUNTER (HEX MHB252 ...

Page 42

... Preliminary specification SAA6712E N-OFFSET HALF CLK COUNTER (HEX ...

Page 43

... Both start counting from the second edge of VHS. The polarity of CLAMP is given with clamp_pol. h_offset Fig.10 RGB data sampling. 43 Preliminary specification SAA6712E VCLK VCLK SAMPLE EDGE dot clock positive 1 dot clock both 2 ...

Page 44

... CLAMP 8.4 Video mode and synchronization signal detection The SAA6712E can be used to build up auto-scan systems using an external microcontroller. Therefore information about the input resolution and timing are provided (see Tables 5 and 6). The flags pos_vsync and pos_hsync show the polarity of the synchronization signals at VVS and VHS ...

Page 45

... RSC 8.5.2 I NITIALIZATION OF EXTERNAL MEMORY All SGRAM and SDRAM devices must be powered-up and initialized correctly. The SAA6712E memory interface is implemented to fulfil the INTEL PC100 SDRAM specification. Table 11 shows the required programming steps to initialize the memory correctly. 1999 Aug 25 To reach a high effective bandwidth all access to the external memory is organized in bursts ...

Page 46

... Philips Semiconductors XGA RGB to TFT graphics engine Table 11 Memory initialization programming STEP 1 SAA6712E Power-on reset 2 set-up timing parameters 3 start memory initialization with setting memory_init 4 set-up all other parameters 5 release internal memory reset together with other internal resets 8.5.3 F RAME RECOVERY Output frames with the right vertical and horizontal dimensions must be generated ...

Page 47

... If the input frame is to large only the right and bottom part will be cropped. The colour of the generated border region must be set via border_colour_red, border_colour_green, and border_colour_blue. C-bus write addresses pic_v_offset pic_h_offset OUTPUT FRAME Fig.12 Picture positioning. 47 Preliminary specification SAA6712E Panning unit out_v_size out_h_size MHB257 ...

Page 48

... The sampling of the ports ovl0 and ovl1 is done on the positive edge of OVCLK in the event that sample_edge is asserted, otherwise on the falling edge of OVCLK. ovl_hs_latency ovl_hs_start ovl_v_offset OVERLAY WINDOW OUTPUT FRAME Fig.13 Overlay window positioning. 48 Preliminary specification SAA6712E ovl_h_length MHB258 ...

Page 49

... If the colour correction unit is switched to bypass mode (when colour_correction_on is not asserted), the incoming colours are used for further processing. Writing to the colour correction table is possible during data processing. 49 Preliminary specification SAA6712E MHB259 2 C-bus ...

Page 50

... A logic 1 selects 24 24 font, and a logic 0 the smaller 12 16 font. If the small 12 128 different characters can be defined. Alternatively characters of the larger 24 Table 12 gives some possible OSD settings. 50 Preliminary specification SAA6712E osd_v_size MHB260 24 character 16 font is used font can be used. ...

Page 51

... Table 5). The definition of a character is done with 3 bytes per line at 24 (72 bytes per character), and with 3 bytes per 2 lines font (24 bytes per character), see Fig.16. 51 Preliminary specification SAA6712E EFFECT 0 OSD character colours are displayed instead of the picture colours 1 OSD character colours defined as ...

Page 52

... Fig.16 Character matrix organization. 8.11 Temporal dithering (frame rate controller) The SAA6712E is able to display true colour (8 bits per colour) on high colour displays (6 bits per colour). The algorithm used is temporal dithering. This feature can be enabled by setting frc_on to logic 1 in the general configuration register block (see Table 5) ...

Page 53

... The border colour inserted by the output interface is the same as the blank colour in the memory interface; blank_colour_red, blank_colour_green, blank_colour_blue. PHS blanking active video border h_active_start Fig.17 Output frame and timing. 53 Preliminary specification SAA6712E h_len_blank h_de_end h_len_border h_max_len h_len_active MHB262 ...

Page 54

... XGA RGB to TFT graphics engine 8.12.3 T IMING REFERENCE SIGNALS The SAA6712E supports three timing reference signals to drive the panels: PVS (vertical synchronization pulse), PHS (horizontal synchronization pulse) and PDE (data qualifier). The polarity of these signals is programmable. To program high polarity the three programming registers (vsync_pol, hsync_pol, de_pol) must be set to logic 1 ...

Page 55

... HIGH-level output OH(LVTTL) voltage at LVTTL pins 1999 Aug unless otherwise specified. amb CONDITIONS MIN. 3.0 3.1 0.5 0.7V DDD 0.5 2.0 outputs at 3-state SDA sink current SDA sink current 2.4 0.85V 55 Preliminary specification SAA6712E TYP. MAX. 3.3 3.6 600 tbf 2 3.3 3.5 tbf tbf tbf 2 +0.3V DDD V + 0.5 V DDD +0 0.5 V ...

Page 56

... PD(o) 1999 Aug see Fig.18; unless otherwise specified. amb CONDITIONS 24 40 single ADC mode 25 double ADC mode 12 6.0 56 Preliminary specification SAA6712E MIN. TYP. MAX. 70 MHz 150 MHz 75 MHz 4 MHz ...

Page 57

... Notes 15pF and 15pF and 10pF and 1999 Aug 25 CONDITIONS = Preliminary specification SAA6712E MIN. TYP. MAX. 125 MHz 125 MHz 6 6 ...

Page 58

... MCLKI MCLKO 1999 Aug 25 t su(i) t h(i) data data transition valid period t h(o) t PD(o) Fig.18 Data timing diagram Fig.19 Memory clock timing. 58 Preliminary specification SAA6712E 1.5 V MHB490 1.5 V MHB491 ...

Page 59

... Philips Semiconductors XGA RGB to TFT graphics engine 12 APPLICATION INFORMATION handbook, full pagewidth VGA TDA8752 PORT 1999 Aug 25 SDRAM SDRAM SDRAM 16 MBits 16 MBits 16 MBits RGB SAA6712E PANEL PORT Fig.20 Test board. 59 Preliminary specification SAA6712E EEPROM MICROCONTROLLER P87C695 2 I C-bus USB MHB457 ...

Page 60

... scale 27.2 24.7 27.2 24.7 4.0 1.27 26.8 24.0 26.8 24.0 3.9 REFERENCES JEDEC EIAJ 60 Preliminary specification detail 1.84 1.84 0.15 0.35 0.3 1.04 1.04 EUROPEAN PROJECTION SAA6712E SOT489 ISSUE DATE 98-05-06 ...

Page 61

... Use a low voltage ( less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds 300 C. When using a dedicated tool, all other leads can be soldered in one operation within seconds between 270 and 320 C. 61 Preliminary specification SAA6712E ...

Page 62

... Wave soldering is only suitable for SSOP and TSSOP packages with a pitch (e) equal to or larger than 0.65 mm definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5 mm. 1999 Aug 25 SOLDERING METHOD WAVE not suitable (2) not suitable suitable (3)(4) not recommended (5) not recommended 62 Preliminary specification SAA6712E (1) REFLOW suitable suitable suitable suitable suitable ...

Page 63

... Philips. This specification can be ordered using the code 9398 393 40011. 1999 Aug 25 C COMPONENTS 2 C components conveys a license under the Philips’ system provided the system conforms to the I 63 Preliminary specification SAA6712E 2 C patent to use the 2 C specification defined by ...

Page 64

Philips Semiconductors – a worldwide company Argentina: see South America Australia: 3 Figtree Drive, HOMEBUSH, NSW 2140, Tel. +61 2 9704 8141, Fax. +61 2 9704 8139 Austria: Computerstr. 6, A-1101 WIEN, P.O. Box 213, Tel. + 101 ...