AT89C5130A-PUTUM Atmel, AT89C5130A-PUTUM Datasheet - Page 122

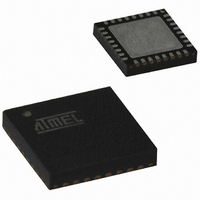

AT89C5130A-PUTUM

Manufacturer Part Number

AT89C5130A-PUTUM

Description

IC 8051 MCU FLASH 16K USB 32QFN

Manufacturer

Atmel

Series

AT89C513xr

Datasheet

1.AT89C5130A-PUTUM.pdf

(188 pages)

Specifications of AT89C5130A-PUTUM

Core Processor

C52X2

Core Size

8-Bit

Speed

48MHz

Connectivity

I²C, SPI, UART/USART, USB

Peripherals

LED, POR, PWM, WDT

Number Of I /o

18

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Eeprom Size

4K x 8

Ram Size

1.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-VQFN Exposed Pad, 32-HVQFN, 32-SQFN, 32-DHVQFN

Package

32QFN EP

Device Core

8051

Family Name

89C

Maximum Speed

48 MHz

Operating Supply Voltage

3.3|5 V

Data Bus Width

8 Bit

Number Of Programmable I/os

34

Interface Type

SPI/TWI/UART/USB

Number Of Timers

3

Processor Series

AT89x

Core

8051

Data Ram Size

1.25 KB

Maximum Clock Frequency

48 MHz

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

AT89STK-05

Minimum Operating Temperature

- 40 C

Height

0.95 mm

Length

7 mm

Supply Voltage (max)

5.5 V

Supply Voltage (min)

2.7 V

Width

7 mm

For Use With

AT89OCD-01 - USB EMULATOR FOR AT8XC51 MCU

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Data Converters

-

Lead Free Status / Rohs Status

Details

Other names

AT89C5130A-PUTIM

AT89C5130A-PUTIM

AT89C5130A-PUTIM

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT89C5130A-PUTUM

Manufacturer:

Atmel

Quantity:

5

Figure 21-3. UFI Block Diagram

Figure 21-4. Minimum Intervention from the USB Device Firmware

21.2

21.2.1

122

Configuration

AT89C5130A/31A-M

HOST

UFI

C51

IN Transactions:

HOST

UFI

C51

General Configuration

OUT Transactions:

DPLL

SIE

OUT DATA0 (n bytes)

IN

Endpoint FIFO write

NACK

• USB controller enable

• Set address

Before any USB transaction, the 48 MHz required by the USB controller must be correctly

generated (See “Clock Controller” on page 14.).

The USB controller will be then enabled by setting the EUSB bit in the USBCON register.

After a Reset or a USB reset, the software has to set the FEN (Function Enable) bit in the

USBADDR register. This action will allow the USB controller to answer to the requests sent

at the address 0.

When a SET_ADDRESS request has been received, the USB controller must only answer

to the address defined by the request. The new address will be stored in the USBADDR reg-

ister. The FEN bit and the FADDEN bit in the USBCON register will be set to allow the USB

controller to answer only to requests sent at the new address.

FIU

DPR Control

USB Side

Transfer

Control

FSM

ACK

Asynchronous Information

Transfer

IN

interrupt C51

User DPRAM

DATA1

Endpoint FIFO read (n bytes)

OUT

Endpoint 6

Endpoint 5

Endpoint 4

Endpoint 3

Endpoint 2

Endpoint 1

Endpoint 0

DATA1

IN

NACK

CSREG 0 to 7

DPR Control

mP side

DATA1

Registers

Bank

OUT

ACK

interrupt C51

DATA1

C51

Microcontroller

Interface

Up to 48 MHz

UC_sysclk

Endpoint FIFO write

ACK

4337K–USB–04/08