R5F212BASNFA#U0 Renesas Electronics America, R5F212BASNFA#U0 Datasheet - Page 64

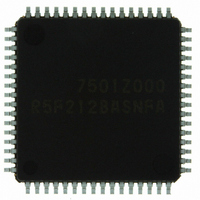

R5F212BASNFA#U0

Manufacturer Part Number

R5F212BASNFA#U0

Description

IC R8C/2B MCU FLASH 96+2K 64LQFP

Manufacturer

Renesas Electronics America

Series

R8C/2x/2Br

Datasheet

1.R5F212B7SNFPU0.pdf

(66 pages)

Specifications of R5F212BASNFA#U0

Core Processor

R8C

Core Size

16/32-Bit

Speed

20MHz

Connectivity

I²C, LIN, SIO, SSU, UART/USART

Peripherals

POR, PWM, Voltage Detect, WDT

Number Of I /o

55

Program Memory Size

96KB (96K x 8)

Program Memory Type

FLASH

Ram Size

7K x 8

Voltage - Supply (vcc/vdd)

2.2 V ~ 5.5 V

Data Converters

A/D 12x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 85°C

Package / Case

64-LQFP

For Use With

R0K5212D8S001BE - KIT STARTER FOR R8C/2DR0K5212D8S000BE - KIT DEV FOR R8C/2D

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

R5F212BASNFA#U0R5F212BASNFA#V2

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Rev.

0.30

1.00

2.00

REVISION HISTORY

Dec 22, 2006

Feb 09, 2007

Oct 17, 2007

Date

All pages “Preliminary” deleted

All pages “PTLG0064JA-A (64F0G) package” added

19 to 20 Figure 3.1 and Figure 3.2 revised

6 to 7

Page

3, 5

19

37

17

18

19

23

31

32

37

44

46

48

50

52

53

54

10

11

24

3

5

6

7

8

Table 4.1;

• 000Ah: “00XXX000b” → “00h” revised

• 0008h: “Module Standby Control Register” → “Module Operation Enable Register” revised

• 000Fh: “00011111b” → “00X11111b” revised

Table 5.11 revised

Table 1.2 revised

Table 1.4 revised

Table 1.5 and Figure 1.1 revised

Table 1.6 and Figure 1.2 revised

Figure 3.1 revised

Figure 3.2 revised

Table 4.1;

• 0008h: “Module Standby Control Register” → “Module Operation Enable Register” revised

• 000Ah: “00XXX000b” → “00h” revised

• 000Fh: “00011111b” → “00X11111b” revised

• 002Bh: “High-Speed On-Chip Oscillator Control Register 6” added

Table 4.5;

Table 5.2 revised

Table 5.3 and Table 5.4; NOTE1 revised

Table 5.11 revised

Table 5.17 revised

Table 5.21 and Figure 5.11; “i = 0 to 2” revised

Table 5.24 revised

Table 5.28 revised, Figure 5.16 “i = 0 to 2” revised

Table 5.31 revised

Table 5.34 revised

Table 5.35 and Figure 5.21; “i = 0 to 2” revised

Table 1.2 and Table 1.4;

• Operating Ambient Temperature: Y version added

• Package: 64-pin FLGA added

Table 1.5 and Figure 1.1 revised

Table 1.6 and Figure 1.2 revised

Figure 1.4 “64-pin LQFP Package” added

Figure 1.5 added

Table 4.4;

0105h: “LIN Control Register 2” register name revised

00F5h: “00h” → “000000XXb” revised

R8C/2A Group, R8C/2B Group Datasheet

A - 2

Description

Summary