PCF8576CHL/1,118 NXP Semiconductors, PCF8576CHL/1,118 Datasheet - Page 18

PCF8576CHL/1,118

Manufacturer Part Number

PCF8576CHL/1,118

Description

IC LCD DRIVER 64LQFP

Manufacturer

NXP Semiconductors

Datasheet

1.PCF8576CTT1118.pdf

(57 pages)

Specifications of PCF8576CHL/1,118

Display Type

LCD

Configuration

Multiple

Interface

I²C

Current - Supply

120µA

Voltage - Supply

2 V ~ 6 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

*

Package / Case

*

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Digits Or Characters

-

Lead Free Status / Rohs Status

Details

Other names

935290305118

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PCF8576CHL/1,118

Manufacturer:

NXP Semiconductors

Quantity:

10 000

NXP Semiconductors

PCF8576C

Product data sheet

7.5.1 Internal clock

7.5.2 External clock

7.5 Oscillator

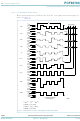

7.6 Timing

The internal logic and the LCD drive signals of the PCF8576C are timed by the frequency

f

f

The clock frequency (f

for data reception from the I

rate of 100 kHz, f

The internal oscillator is enabled by connecting pin OSC to pin V

output from pin CLK is the clock signal for any cascaded PCF8576C in the system.

Connecting pin OSC to V

external clock input.

Remark: A clock signal must always be supplied to the device. Removing the clock,

freezes the LCD in a DC state, which is not suitable for the liquid crystal.

The timing of the PCF8576C sequences the internal data flow of the device. This includes

the transfer of display data from the display RAM to the display segment outputs. In

cascaded applications, the synchronization signal (SYNC) maintains the correct timing

relationship between the PCF8576Cs in the system. The timing also generates the LCD

frame frequency which is derived as an integer division of the clock frequency (see

Table

internal clock is used or by the frequency applied to the pin CLK when an external clock is

used.

Table 6.

[1]

[2]

[3]

The ratio between the clock frequency and the LCD frame frequency depends on the

power mode in which the device is operating. In the power-saving mode the reduction

ratio is six times smaller; this allows the clock frequency to be reduced by a factor of six.

The reduced clock frequency results in a significant reduction in power consumption.

PCF8576C mode

Normal-power mode

Power-saving mode

clk

clk(ext)

, which equals either the built-in oscillator frequency f

The possible values for f

For f

For f

6). The frame frequency is set by the mode-set command (see

.

clk

clk

= 200 kHz.

= 31 kHz.

LCD frame frequencies

All information provided in this document is subject to legal disclaimers.

clk

should be chosen to be above 125 kHz.

clk

Rev. 10 — 22 July 2010

clk

) determines the LCD frame frequency (f

DD

see

2

enables an external clock source. Pin CLK then becomes the

C-bus. To allow I

Frame frequency

f

f

Table

fr

fr

=

=

[1]

------------ -

2880

--------- -

480

16.

f

f

clk

clk

Universal LCD driver for low multiplex rates

2

C-bus transmissions at their maximum data

osc

Nominal frame frequency (Hz)

69

65

or the external clock frequency

[2]

[3]

fr

SS

) and the maximum rate

. In this case, the

PCF8576C

Table

© NXP B.V. 2010. All rights reserved.

9) when an

18 of 57