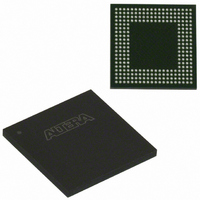

EPM570ZM256C6N Altera, EPM570ZM256C6N Datasheet - Page 13

EPM570ZM256C6N

Manufacturer Part Number

EPM570ZM256C6N

Description

IC MAX IIZ CPLD 570 LE 256-MBGA

Manufacturer

Altera

Series

MAX® IIr

Specifications of EPM570ZM256C6N

Programmable Type

In System Programmable

Delay Time Tpd(1) Max

9.0ns

Voltage Supply - Internal

1.71 V ~ 1.89 V

Number Of Logic Elements/blocks

570

Number Of Macrocells

440

Number Of I /o

160

Operating Temperature

0°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

256-MBGA

Voltage

1.8V

Memory Type

FLASH

Number Of Logic Elements/cells

570

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Other names

544-2453

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EPM570ZM256C6N

Manufacturer:

ALTERA

Quantity:

736

Chapter 2: MAX II Architecture

Logic Array Blocks

Figure 2–4. DirectLink Connection

LAB Control Signals

© October 2008 Altera Corporation

DirectLink interconnect from

left LAB or IOE output

Each LAB contains dedicated logic for driving control signals to its LEs. The control

signals include two clocks, two clock enables, two asynchronous clears, a

synchronous clear, an asynchronous preset/load, a synchronous load, and

add/subtract control signals, providing a maximum of 10 control signals at a time.

Although synchronous load and clear signals are generally used when implementing

counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB’s clock and

clock enable signals are linked. For example, any LE in a particular LAB using the

labclk1 signal also uses labclkena1. If the LAB uses both the rising and falling

edges of a clock, it also uses both LAB-wide clock signals. Deasserting the clock

enable signal turns off the LAB-wide clock.

Each LAB can use two asynchronous clear signals and an asynchronous load/preset

signal. By default, the Quartus II software uses a NOT gate push-back technique to

achieve preset. If you disable the NOT gate push-back option or assign a given register

to power-up high using the Quartus II software, the preset is then achieved using the

asynchronous load signal with asynchronous load data input tied high.

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder

and subtractor. This saves LE resources and improves performance for logic functions

such as correlators and signed multipliers that alternate between addition and

subtraction depending on data.

The LAB column clocks [3..0], driven by the global clock network, and LAB local

interconnect generate the LAB-wide control signals. The MultiTrack interconnect

structure drives the LAB local interconnect for non-global control signal generation.

The MultiTrack interconnect’s inherent low skew allows clock and control signal

distribution in addition to data.

circuit.

interconnect

DirectLink

to left

Interconnect

Local

Logic Element

Figure 2–5

LE0

LE1

LE2

LE3

LE4

LE5

LE6

LE7

LE8

LE9

LAB

shows the LAB control signal generation

DirectLink

interconnect

to right

DirectLink interconnect from

right LAB or IOE output

MAX II Device Handbook

2–5