DSPB56362AG120 Freescale Semiconductor, DSPB56362AG120 Datasheet - Page 65

DSPB56362AG120

Manufacturer Part Number

DSPB56362AG120

Description

IC DSP 24BIT AUD 120MHZ 144-LQFP

Manufacturer

Freescale Semiconductor

Series

Symphony™r

Type

Audio Processorr

Datasheet

1.DSPB56362AG120.pdf

(152 pages)

Specifications of DSPB56362AG120

Interface

Host Interface, I²C, SAI, SPI

Clock Rate

120MHz

Non-volatile Memory

ROM (126 kB)

On-chip Ram

42kB

Voltage - I/o

3.30V

Voltage - Core

3.30V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

144-LQFP

Device Core Size

24b

Architecture

Modified Harvard

Format

Fixed Point

Clock Freq (max)

120MHz

Mips

120

Device Input Clock Speed

120MHz

Ram Size

42KB

Program Memory Size

90KB

Operating Supply Voltage (typ)

3.3V

Operating Supply Voltage (min)

3.14V

Operating Supply Voltage (max)

3.46V

Operating Temp Range

-40C to 105C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

144

Package Type

LQFP

Product

DSPs

Data Bus Width

24 bit

Processor Series

DSP563xx

Core

56000

Numeric And Arithmetic Format

Fixed-Point

Instruction Set Architecture

Modified Harvard

Device Million Instructions Per Second

120 MIPS

Maximum Clock Frequency

120 MHz

Program Memory Type

Flash

Data Ram Size

42 KB

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 105 C

Mounting Style

SMD/SMT

Interface Type

SPI, I2C, ESAI, SHI

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DSPB56362AG120

Manufacturer:

FSC

Quantity:

12 000

Company:

Part Number:

DSPB56362AG120

Manufacturer:

FREESCA

Quantity:

273

Company:

Part Number:

DSPB56362AG120

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

DSPB56362AG120

Manufacturer:

N/A

Quantity:

20 000

Freescale Semiconductor

1

2

3

4

5

209

210

211

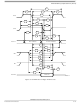

External bus synchronous timings should be used only for reference to the clock and not for relative timings.

WS is the number of wait states specified in the BCR.

The asynchronous delays specified in the expressions are valid for DSP56362.

T198 and T199 are valid for Address Trace mode if the ATE bit in the OMR is set. Use the status of BR (See T212) to

determine whether the access referenced by A0–A23 is internal or external, when this mode is enabled

If WS > 1, WR assertion refers to the next rising edge of CLKOUT.

No.

CLKOUT high to RD deassertion

CLKOUT high to WR assertion

CLKOUT high to WR deassertion

Table 3-17 External Bus Synchronous Timings (SRAM Access)

Characteristics

5

DSP56362 Technical Data, Rev. 4

All frequencies:

Expression

0.5 × T

[2 ≤ WS ≤ 3]

External Memory Expansion Port (Port A)

[WS = 1 or

WS ≥ 4]

C

+ 4.3

2

,

1

3

(continued)

Min

0.0

6.3

1.3

0.0

100 MHz

Max

9.3

4.3

3.8

4.0

Unit

ns

ns

ns

3-39