20-668-0003 Rabbit Semiconductor, 20-668-0003 Datasheet - Page 123

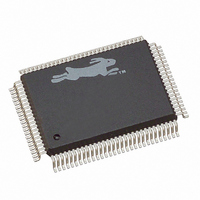

20-668-0003

Manufacturer Part Number

20-668-0003

Description

IC CPU RABBIT2000 30MHZ 100PQFP

Manufacturer

Rabbit Semiconductor

Datasheet

1.20-668-0003.pdf

(228 pages)

Specifications of 20-668-0003

Processor Type

Rabbit 2000 8-Bit

Speed

30MHz

Voltage

2.7V, 3V, 3.3V, 5V

Mounting Type

Surface Mount

Package / Case

100-MQFP, 100-PQFP

Data Bus Width

8 bit

Maximum Clock Frequency

30 MHz

Operating Supply Voltage

0 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Number Of Programmable I/os

40

Number Of Timers

8 & 10 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

20-668-0003

316-1062

316-1062

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

20-668-0003

Manufacturer:

Rabbit Semiconductor

Quantity:

10 000

- Current page: 123 of 228

- Download datasheet (2Mb)

11.2.1 Using Timer B

Normally the prescaler is set to divide

appropriate to the problem. For example, if the clock is 22.1184 MHz, then

11.0592 MHz. A Timer B clock rate of 11.0592 MHz will cause a complete cycle of the

10-bit clock in 92.6 µs.

Normally an interrupt will occur when either of the comparators in Timer B generates a

pulse. The interrupt routine must detect which comparator is responsible for the interrupt

and dispatch the interrupt to a service routine. The service routine sets up the next match

value, which will become the match value after the next interrupt. If the clocked parallel

ports are being used, then a value will normally be loaded into some bits of the parallel

port register. These bits will become the output bits on the next match pulse. (It is neces-

sary to keep a shadow register for the parallel port unless the bit-addressable feature of

ports D and E is used.)

If it is desired to read the time from the Timer B counter, either during an interrupt caused

by the match pulse or in some other interrupt routine asynchronous to the match pulse, a

special procedure needs to be used to read the counter because the upper 2 bits are in a dif-

ferent register than the lower 8 bits. The following method is suggested.

1. Read the lower 8 bits.

2. Read the upper 2 bits

3. Read the lower 8 bits again

4. If bit 7 changed from 1 to 0 between the first and second read of the lower 8 bits there

This procedure assumes that the time between reads can be guaranteed to be less than 256

counts. This can be guaranteed in most systems by disabling the priority 1 interrupts,

which will normally be disabled in any case in an interrupt routine.

It is inadvisable to disable the high-priority interrupts (levels 2 and 3) as that defeats their

purpose.

If speed is critical, the three reads of the registers can be performed without testing for the

carry. The three register values can be saved and the carry test can be performed by a

lower priority analysis routine. Since the upper 2 bits are in the register TBCMR at

address 0x0BE, and the lower 8 bits are in TBCLR at address 0x0BF, both registers can be

read with a single 16-bit I/O instruction. The following sequence illustrates how the regis-

ters could be captured.

Chapter 11 Timers

has been a carry to the upper 2 bits. In this case read the upper 2 bits again and decre-

ment those 2 bits to get the correct upper 2 bits. Use the first read of the lower 8 bits.

; enter from external interrupt on pulse input transition

; 19 clocks latency plus 10 clocks interrupt execution

push af

push hl

ioi ld a,(TBCLR)

ioi ld hl,(TBCMR) ; 13 get l=upper, h=lower

; 7

; 11 get lower 8 bits of counter

PCLK

/2 by a number that provides a counting rate

PCLK

/2 is

117

Related parts for 20-668-0003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC CPU RABBIT4000 128-LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

IC MPU RABIT3000A 55.5MHZ128LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

Microprocessors - MPU Rabbit 3000 TFBGA Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

Microprocessors - MPU Rabbit 4000 LQFP Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

IC, I/O EXPANDER, 8BIT, 40MHZ, TQFP-64

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

SCRs 1.5A 200uA 400V Sensing

Manufacturer:

Littelfuse Inc

Datasheet:

Part Number:

Description:

CARD 6-RELAY SMARTSTAR SR9500

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

ADAPTER 20 PIN .420" PLUGS(6PCS)

Manufacturer:

Logical Systems Inc.

Datasheet:

Part Number:

Description:

CONN BARRIER BLOCK .438" 20 POS

Manufacturer:

Cinch Connectors

Datasheet:

Part Number:

Description:

20 MODII 2PC HDR DR SHRD, ROHS

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet: