20-668-0003 Rabbit Semiconductor, 20-668-0003 Datasheet - Page 47

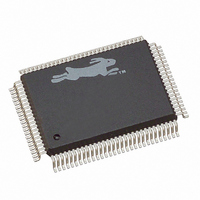

20-668-0003

Manufacturer Part Number

20-668-0003

Description

IC CPU RABBIT2000 30MHZ 100PQFP

Manufacturer

Rabbit Semiconductor

Datasheet

1.20-668-0003.pdf

(228 pages)

Specifications of 20-668-0003

Processor Type

Rabbit 2000 8-Bit

Speed

30MHz

Voltage

2.7V, 3V, 3.3V, 5V

Mounting Type

Surface Mount

Package / Case

100-MQFP, 100-PQFP

Data Bus Width

8 bit

Maximum Clock Frequency

30 MHz

Operating Supply Voltage

0 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Number Of Programmable I/os

40

Number Of Timers

8 & 10 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

20-668-0003

316-1062

316-1062

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

20-668-0003

Manufacturer:

Rabbit Semiconductor

Quantity:

10 000

- Current page: 47 of 228

- Download datasheet (2Mb)

This section describes the various capabilities of the Rabbit that may not be obvious from

the technical description.

4.1 Precisely Timed Output Pulses

The Rabbit can output precise pulses under software control. The effect of interrupt latency

is avoided because the interrupt always prepares a future pulse edge that is clocked into

the output registers on the next clock. This is shown in Figure 4-1.

The timer output in Figure 4-1 is periodic. As long as the interrupt routine can be com-

pleted during one timer period, an arbitrary pattern of synchronous pulses can be output

from the parallel port.

The interrupt latency depends on the priority of the interrupt and the amount of time that

other interrupt routines of the same or higher priority inhibit interrupts. The first instruc-

tion of the interrupt routine will start executing within 30 clocks of the interrupt request

for the highest priority interrupt routine. This includes 19 clocks for the longest instruction

to complete execution and 10 clocks for the interrupt to execute. Pushing registers requires

10–12 clocks per 16-bit register. Popping registers requires 7–9 clocks. Return from inter-

rupt requires 7 clocks. If three registers are saved and restored, and 20 instructions averag-

ing 5 clocks are executed, an entire interrupt routine will require about 200 clocks, or 10

µs with a 20 MHz clock. Given this timing, the following capabilities become possible.

Chapter 4 Rabbit Capabilities

Latency

A

Interrupt

routine sets

Figure 4-1. Timed Output Pulses

B

4. R

Setup Register

ABBIT

C

Timer Output

C

Parallel Port Output

APABILITIES

Parallel Port Output

Timer Output

41

Related parts for 20-668-0003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC CPU RABBIT4000 128-LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

IC MPU RABIT3000A 55.5MHZ128LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

Microprocessors - MPU Rabbit 3000 TFBGA Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

Microprocessors - MPU Rabbit 4000 LQFP Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

IC, I/O EXPANDER, 8BIT, 40MHZ, TQFP-64

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

SCRs 1.5A 200uA 400V Sensing

Manufacturer:

Littelfuse Inc

Datasheet:

Part Number:

Description:

CARD 6-RELAY SMARTSTAR SR9500

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

ADAPTER 20 PIN .420" PLUGS(6PCS)

Manufacturer:

Logical Systems Inc.

Datasheet:

Part Number:

Description:

CONN BARRIER BLOCK .438" 20 POS

Manufacturer:

Cinch Connectors

Datasheet:

Part Number:

Description:

20 MODII 2PC HDR DR SHRD, ROHS

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet: