UMA1021M/C2 Philips Semiconductors (Acquired by NXP), UMA1021M/C2 Datasheet - Page 31

UMA1021M/C2

Manufacturer Part Number

UMA1021M/C2

Description

UDA1380; Stereo Audio Coder-decoder For MD, CD And MP3

Manufacturer

Philips Semiconductors (Acquired by NXP)

Datasheet

1.UMA1021MC2.pdf

(68 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

UMA1021M/C2

Manufacturer:

NXP

Quantity:

3 384

Part Number:

UMA1021M/C2

Manufacturer:

PHILIPS/飞利浦

Quantity:

20 000

Part Number:

UMA1021M/C2.

Manufacturer:

PHILIPS/飞利浦

Quantity:

20 000

Philips Semiconductors

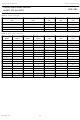

Table 19 Dividers for system clock input

Table 20 WSPLL settings

2003 Apr 04

Stereo audio coder-decoder

for MD, CD and MP3

sys_div1

3 and 2

1 and 0

PLL1

BIT

4

0

0

1

1

0

0

1

1

DAC_CLK

sys_div[1:0]

PLL[1:0]

SYMBOL

sys_div0

PLL0

0

1

0

1

0

1

0

1

DAC clock select. A 1-bit value to select the clocks for the DAC

(interpolator and FSDAC analog block). In both cases the clocks must be

128f

the WSI clock, and in the other case the clock is derived from the SYSCLK.

When this bit is logic 0: SYSCLK is used. When this bit is logic 1: WSPLL is

used. Default value 0.

Dividers for system clock input. A 2-bit value to select the proper division

factor for the SYSCLK input in such a way that a128f

from the SYSCLK clock signal. The 128f

decimator and interpolator. Default value 00, see Table 19.

WSPLL setting. A 2-bit value to select the WSPLL input frequency range.

These set the proper divider setting for the WSPLL. The input is the

WSI signal, the output inside the IC is a 128f

value 10, see Table 20.

s

and 256f

INPUT FREQUENCY RANGE (kHz) ON PIN WSI

s

(for the analog part), but in one case the clock is derived from

31

INPUT CLOCK ON PIN SYSCLK

25 to 50 (default)

DESCRIPTION

256f

6.25 to 12.5

12.5 to 25

50 to 100

s

384f

512f

768f

(default)

s

s

s

s

clock is needed for clocking the

s

and a 256f

s

clock will be generated

s

clock. Default

Product specification

UDA1380