XC68HC705JJ7 Motorola, XC68HC705JJ7 Datasheet - Page 167

XC68HC705JJ7

Manufacturer Part Number

XC68HC705JJ7

Description

MICROCONTROLLER

Manufacturer

Motorola

Datasheet

1.XC68HC705JJ7.pdf

(242 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XC68HC705JJ7CP

Manufacturer:

ON

Quantity:

6 233

Part Number:

XC68HC705JJ7CP

Manufacturer:

MOTOROLA/摩托罗拉

Quantity:

20 000

- Current page: 167 of 242

- Download datasheet (3Mb)

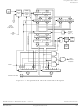

11.6 Output Compare Registers

MC68HC705JJ7 • MC68HC705JP7 — REV 4

MOTOROLA

NOTE:

The result obtained by an input capture will be one count higher than the

value of the free-running timer counter preceding the external transition.

This delay is required for internal synchronization. Resolution is affected

by the prescaler, allowing the free-running timer counter to increment

once every four internal clock cycles (eight oscillator clock cycles).

Reading the ICRH inhibits future captures until the ICRL is also read.

Reading the ICRL after reading the timer status register (TSR) clears the

ICF flag bit. There is no conflict between reading the ICRL and transfers

from the free-running timer counters. The input capture registers always

contain the free-running timer counter value which corresponds to the

most recent input capture.

To prevent interrupts from occurring between readings of the ICRH and

ICRL, set the I bit in the condition code register (CCR) before reading

ICRH and clear the I bit after reading ICRL.

The output compare function is a means of generating an output signal

when the 16-bit timer counter reaches a selected value as shown in

Figure

registers. On every fourth internal clock cycle (every eight oscillator

clock cycles) the output compare circuitry compares the value of the

free-running timer counter to the value written in the output compare

registers. When a match occurs, the timer transfers the output level

(OLVL) from the timer control register (TCR) to the PB4/AN4/TCMP pin.

Software can use the output compare register to measure time periods,

to generate timing delays, or to generate a pulse of specific duration

or a pulse train of specific frequency and duty cycle on the

PB4/AN4/TCMP pin.

The planned action on the PB4/AN4/TCMP pin depends on the value

stored in the OLVL bit in the TCR, and it occurs when the value of the

16-bit free-running timer counter matches the value in the output

compare registers shown in

bits and are unaffected by reset.

11-8. Software writes the selected value into the output compare

Programmable Timer

Figure

11-9. These registers are read/write

Output Compare Registers

Programmable Timer

Advance Information

167

Related parts for XC68HC705JJ7

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Motorola, Inc [VOLTAGE REGULATOR]

Manufacturer:

Motorola

Datasheet:

Part Number:

Description:

3N2046367254 MOTOROLA SC (XSTRS/R F)

Manufacturer:

Motorola

Datasheet:

Part Number:

Description:

MOTOROLA POWERPC 603e MICROPROCESSOR

Manufacturer:

Motorola

Part Number:

Description:

Motorola Semiconductor Datasheet Library

Manufacturer:

Motorola

Part Number:

Description:

SWITCHMODE Schottky Power Rectifier(POWERTAP III Package)

Manufacturer:

Motorola

Datasheet:

Part Number:

Description:

SWITCHMODE Schottky Power Rectifirer

Manufacturer:

Motorola

Datasheet:

Part Number:

Description:

Hybrid Power Module

Manufacturer:

Motorola

Datasheet:

Part Number:

Description:

Hybrid Power Module

Manufacturer:

Motorola

Datasheet:

Part Number:

Description:

Search -----> MTE53N50E

Manufacturer:

Motorola

Datasheet:

Part Number:

Description:

Hybrid Power Module

Manufacturer:

Motorola

Datasheet:

Part Number:

Description:

Hybrid Power Module

Manufacturer:

Motorola

Datasheet:

Part Number:

Description:

SCHOTTKY BARRIER RECTIFIER 200 AMPERES 60 VOLT

Manufacturer:

Motorola

Datasheet:

Part Number:

Description:

NPN SILICON POWER DARLINGTON TRANSISTOR

Manufacturer:

Motorola

Datasheet: