ISL6556ACR Intersil, ISL6556ACR Datasheet

ISL6556ACR

Specifications of ISL6556ACR

Available stocks

Related parts for ISL6556ACR

ISL6556ACR Summary of contents

Page 1

... ISL6556ACBZ SOIC (Note) (Pb-free) ISL6556ACR 5x5B QFN L32.5x5B ISL6556ACRZ 5x5B QFN (Note) (Pb-free) NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020C ...

Page 2

Pinouts 32 LEAD QFN TOP VIEW VID3 1 2 VID2 VID1 3 VID0 4 5 VID12.5 6 OFS DAC 7 REF ISL6556A PWM4 ...

Page 3

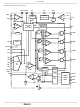

ISL6565ACR Block Diagram VDIFF PGOOD RGND x1 VSEN OVP +200mV OFS OFFSET OFSOUT REF DAC VID4 VID3 DYNAMIC VID2 VID VID1 D/A VID0 VID12.5 COMP FB 3 ISL6556A OVP VCC OVP R S POWER-ON LATCH RESET (POR) Q SOFT START ...

Page 4

Typical Application of ISL6556ACB +5V COMP VCC FB DAC VDIFF VSEN REF RGND PGOOD OVP ISEN1 ISL6556ACB VID4 PWM1 VID3 PWM2 VID2 ISEN2 VID1 PWM3 VID0 ISEN3 VID12.5 PWM4 OFS FS ISEN4 GND VID_PGOOD (BUFFERED) 4 ISL6556A ...

Page 5

... Typical Application of ISL6556ACR +5V FB COMP VCC EN VDIFF DAC VSEN RGND REF PGOOD OVP OFSOUT ISL6556ACR VID4 ISEN1 VID3 PWM1 VID2 PWM2 ISEN2 VID1 PWM3 VID0 ISEN3 VID12.5 PWM4 OFS FS ISEN4 ENLL EN GND R T VID_PGOOD 5 ISL6556A +12V VCC BOOT UGATE PVCC PHASE ...

Page 6

ISL6565ACB Block Diagram VDIFF PGOOD RGND x1 VSEN OVP +200mV OFS OFFSET REF DAC VID4 VID3 DYNAMIC VID2 VID VID1 D/A VID0 VID12.5 COMP FB 6 ISL6556A OVP VCC OVP R S POWER-ON LATCH RESET (POR) Q SOFT START CLOCK ...

Page 7

... VCC = 5VDC 0VDC 100kΩ T VCC tied to 12VDC through 300Ω resistor, R VCC tied to 12VDC through 300Ω resistor, R VCC Rising VCC Falling EN Rising Hysteresis Fault Reset ENLL = 5V (Note 5) (Note 5) VID = 010100 (ISL6556ACR Only) θ θ (°C/ 0°C to 105°C. J MIN TYP MAX - ...

Page 8

Electrical Specifications Operating Conditions: VCC = 5V or ICC < 25mA (Note 4), T Unless Otherwise Specified. (Continued) PARAMETER PIN-ADJUSTABLE OFFSET Voltage at OFS pin OSCILLATOR Accuracy Adjustment Range Sawtooth Amplitude Max Duty Cycle ERROR AMPLIFIER Open-Loop Gain Open-Loop Bandwidth ...

Page 9

... Dynamic VID™ operations. PWM1, PWM2, PWM3, PWM4 Pulse-width modulation outputs. Connect these pins to the PWM input pins of the Intersil driver IC. The number of active channels is determined by the state of PWM3 and PWM4. Tie PWM3 to VCC to configure for 2-phase operation. Tie PWM4 to VCC to configure for 3-phase operation ...

Page 10

... ISL6556A controller helps in simplifying the implementation by integrating vital functions and requiring minimal output components. The block diagrams on pages 2 and 3 provide top level views of multi-phase power conversion using the ISL65556ACB and ISL6556ACR controllers. IL1 + IL2 + IL3, 7A/DIV IL3, 7A/DIV PWM3, 5V/DIV PWM2, 5V/DIV ...

Page 11

RMS input capacitor current. The single-phase converter must use an input capacitor bank with twice the RMS current capacity as the equivalent three- phase converter. INPUT-CAPACITOR CURRENT, 10A/DIV CHANNEL 3 Channel 3 INPUT CURRENT input current 10A/DIV ...

Page 12

... ISL6556A to include the combined tolerances of each of these elements. PWM1 The output of the error amplifier, V sawtooth waveform to generate the PWM signals. The PWM signals control the timing of the Intersil MOSFET drivers and regulate the converter output to the specified reference voltage. The internal and external circuitry that controls Σ ...

Page 13

VSEN, and inverting input, RGND, of the remote-sense amplifier. The remote-sense output, V connected to the inverting input of the error amplifier through an external resistor. A digital to analog converter (DAC) generates a reference voltage based on ...

Page 14

... These functions are shown in Figures 6 and 7. As evident in Figure 7, the OFSOUT pin must be connected to the REF pin for this current injection to function in ISL6556ACR. The current flowing through R offset at the REF pin, which is ultimately duplicated at the output of the regulator. Once the desired output offset voltage has been determined, ...

Page 15

... The schematic in Figure 8 demonstrates sequencing the ISL6556A with the HIP660X family of Intersil MOSFET drivers, which require (EQ. 9) 12V bias. 3. (ISL6556ACR only) The voltage on ENLL must be logic high to enable the controller. This pin is typically is 22nF based connected to the VID_PGOOD. The ISL6556ACB has REF this signal internally connected high ...

Page 16

Soft-Start During soft start, the DAC voltage ramps linearly from zero to the programmed VID level. The PWM signals remain in the high-impedance state until the controller detects that the ramping DAC level has reached the output-voltage level. This protects ...

Page 17

... VSEN falls below 0.6V with valid VCC or 1.5V otherwise. This causes the Intersil drivers to turn on the lower MOSFETs and pull the output voltage below a level that might cause damage to the load. The PWM outputs remain low until VDIFF falls to the programmed DAC level when they enter a high-impedance state ...

Page 18

MOSFETs, inductors and heat-dissipating surfaces. MOSFETs The choice of MOSFETs depends on the current each MOSFET will be required to conduct; the switching frequency; the capability of the MOSFETs to dissipate ...

Page 19

---------- ΔT ISEN 2 , ISEN 1 the measured temperature rise above the ambient temperature. While a single adjustment according to Equation 18 is usually sufficient, it may occasionally be necessary to adjust R two ...

Page 20

V the peak-to-peak sawtooth signal amplitude as described in Figure 4 and Electrical Specifications. Once selected, the compensation values in Equations 21 assure a stable converter with reasonable transient performance. In most cases, ...

Page 21

Output Filter Design. Choose the lowest switching frequency that allows the regulator to meet the transient-response requirements. 1000 100 10 10 100 SWITCHING FREQUENCY (kHz) FIGURE 13 SWITCHING FREQUENCY T Switching frequency is ...

Page 22

0.5 I L, 0.75 I L,PP O L,PP 0.2 0 0.2 0.4 0.6 DUTY CYCLE (V O FIGURE 16. NORMALIZED INPUT-CAPACITOR RMS CURRENT vs DUTY ...

Page 23

... Align the output inductors and MOSFETs such that space between the components is minimized while creating the PHASE plane. Place the Intersil MOSFET driver IC as close as possible to the MOSFETs they control to reduce the parasitic impedances due to trace length between critical driver input and output signals ...

Page 24

Small Outline Plastic Packages (SOIC) N INDEX 0.25(0.010) H AREA E - SEATING PLANE - -C- α 0.10(0.004) 0.25(0.010 NOTES: 1. Symbols are defined in the ...

Page 25

... Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use ...