C8051F321-GM Silicon Laboratories Inc, C8051F321-GM Datasheet - Page 154

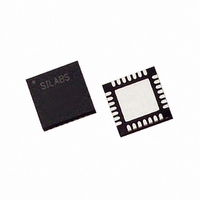

C8051F321-GM

Manufacturer Part Number

C8051F321-GM

Description

IC 8051 MCU 16K FLASH 28MLP

Manufacturer

Silicon Laboratories Inc

Series

C8051F32xr

Datasheets

1.C8051F320-TB.pdf

(250 pages)

2.C8051F321-GMR.pdf

(2 pages)

3.C8051F321-GM.pdf

(256 pages)

Specifications of C8051F321-GM

Program Memory Type

FLASH

Program Memory Size

16KB (16K x 8)

Package / Case

28-VQFN Exposed Pad, 28-HVQFN, 28-SQFN, 28-DHVQFN

Core Processor

8051

Core Size

8-Bit

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART, USB

Peripherals

Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT

Number Of I /o

21

Ram Size

2.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 13x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

C8051F3x

Core

8051

Data Bus Width

8 bit

Data Ram Size

2.25 KB

Interface Type

I2C/SMBus/SPI/UART/USB

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

21

Number Of Timers

4

Operating Supply Voltage

2.7 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051F320DK

Minimum Operating Temperature

- 40 C

On-chip Adc

13-ch x 10-bit or 17-ch x 10-bit

No. Of I/o's

21

Ram Memory Size

1280Byte

Cpu Speed

25MHz

No. Of Timers

4

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

336-1480 - DAUGHTER CARD TOOLSTCK C8051F321770-1006 - ISP 4PORT FOR SILABS C8051F MCU336-1449 - ADAPTER PROGRAM TOOLSTICK F321336-1260 - DEV KIT FOR C8051F320/F321

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1261

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

C8051F321-GM

Manufacturer:

SiliconL

Quantity:

4 364

Part Number:

C8051F321-GM

Manufacturer:

SILICON LABS/芯科

Quantity:

20 000

Part Number:

C8051F321-GMR

Manufacturer:

SILICON LABS/芯科

Quantity:

20 000

C8051F320/1

15.7. Function Configuration and Control

The USB register POWER (Figure 15.11) is used to configure and control USB0 at the device level (enable/disable,

Reset/Suspend/Resume handling, etc.).

USB Reset: The USBRST bit (POWER.3) is set to ‘1’ by hardware when Reset signaling is detected on the bus.

Upon this detection, the following occur:

Writing a ‘1’ to the USBRST bit will generate an asynchronous USB0 reset. All USB registers are reset to their

default values following this asynchronous reset.

Suspend Mode: With Suspend Detection enabled (SUSEN = ‘1’), USB0 will enter Suspend Mode when Suspend

signaling is detected on the bus. An interrupt will be generated if enabled (SUSINTE = ‘1’). The Suspend Interrupt

Service Routine (ISR) should perform application-specific configuration tasks such as disabling appropriate peripher-

als and/or configuring clock sources for low power modes. See

details on internal oscillator configuration, including the Suspend mode feature of the internal oscillator.

USB0 exits Suspend mode when any of the following occur: (1) Resume signaling is detected or generated, (2) Reset

signaling is detected, or (3) a device or USB reset occurs. If suspended, the internal oscillator will exit Suspend mode

upon any of the above listed events.

Resume Signaling: USB0 will exit Suspend mode if Resume signaling is detected on the bus. A Resume interrupt

will be generated upon detection if enabled (RESINTE = ‘1’). Software may force a Remote Wakeup by writing ‘1’

to the RESUME bit (POWER.2). When forcing a Remote Wakeup, software should write RESUME = ‘0’ to end

Resume signaling 10-15 ms after the Remote Wakeup is initiated (RESUME = ‘1’).

ISO Update: When software writes ‘1’ to the ISOUP bit (POWER.7), the ISO Update function is enabled. With ISO

Update enabled, new packets written to an ISO IN endpoint will not be transmitted until a new Start-Of-Frame (SOF)

is received. If the ISO IN endpoint receives an IN token before a SOF, USB0 will transmit a zero-length packet.

When ISOUP = ‘1’, ISO Update is enabled for all ISO endpoints.

USB Enable: USB0 is disabled following a Power-On-Reset (POR). USB0 is enabled by clearing the USBINH bit

(POWER.4). Once written to ‘0’, the USBINH can only be set to ‘1’ by one of the following: (1) a Power-On-Reset

(POR), or (2) an asynchronous USB0 reset generated by writing ‘1’ to the USBRST bit (POWER.3).

Software should perform all USB0 configuration before enabling USB0. The configuration sequence should be per-

formed as follows:

154

1.

2.

3.

4.

5.

6.

Step 1. Select and enable the USB clock source.

Step 2. Reset USB0 by writing USBRST= ‘1’.

Step 3. Configure and enable the USB Transceiver.

Step 4. Perform any USB0 function configuration (interrupts, Suspend detect).

Step 5. Enable USB0 by writing USBINH = ‘0’.

The USB0 Address is reset (FADDR = 0x00).

Endpoint FIFOs are flushed.

Control/status registers are reset to 0x00 (E0CSR, EINCSRL, EINCSRH, EOUTCSRL, EOUTCSRH).

USB register INDEX is reset to 0x00.

All USB interrupts (excluding the Suspend interrupt) are enabled and their corresponding flags cleared.

A USB Reset interrupt is generated if enabled.

Rev. 1.1

Section “13. Oscillators” on page 117

for more