HD64F38024DV Renesas Electronics America, HD64F38024DV Datasheet - Page 56

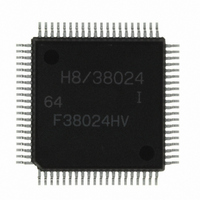

HD64F38024DV

Manufacturer Part Number

HD64F38024DV

Description

IC H8/SLP MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300L SLPr

Datasheets

1.US38024-BAG1.pdf

(684 pages)

2.DF36012GFYV.pdf

(1021 pages)

3.DF38102HV.pdf

(145 pages)

Specifications of HD64F38024DV

Core Processor

H8/300L

Core Size

8-Bit

Speed

10MHz

Connectivity

SCI

Peripherals

LCD, PWM, WDT

Number Of I /o

51

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F38024DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 56 of 1021

- Download datasheet (5Mb)

Table 2.8

Item

Block transfer

instruction

Restriction for

output at

prepro-

cessor

expansion

Message level CHAnge_message

Preferential

allocation of

register

storage class

variables

ANSI

conformance

42

Other Options (cont)

Command Line

Format

EEpmov

NOLINe

<sub>:<level>

<level>:{Information

ENAble_register

STRIct_ansi

=<sub>[,...]

[=<n>[-m],...]

| Warning

| Error }

Dialog Menu

C/C++ <Other>

[Miscellaneous options :]

C/C++ <Other>

[Miscellaneous options :]

source file]

C/C++ <Other>

[User defined options :]

C/C++ <Other>

[Miscellaneous options :]

C/C++ <Other>

[Miscellaneous options :]

strictly]

[Use EEPMOVE in block copy]

[Suppress #line in preprocessed

[Enable register declaration]

[Obey ansi specifications more

Specification

Expands structure

assignment expression by

the eepmov instruction.

Disables #line output at

preprocessor expansion.

Changes message level.

Preferentially allocates

the variables with register

storage class

specification to registers.

Conforms to the ANSI

standard for the following

processing:

Associative rule of

floating-point

operations

Related parts for HD64F38024DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet: