HD64F38024DV Renesas Electronics America, HD64F38024DV Datasheet - Page 969

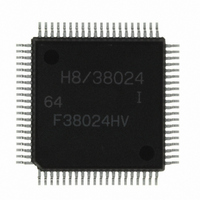

HD64F38024DV

Manufacturer Part Number

HD64F38024DV

Description

IC H8/SLP MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300L SLPr

Datasheets

1.US38024-BAG1.pdf

(684 pages)

2.DF36012GFYV.pdf

(1021 pages)

3.DF38102HV.pdf

(145 pages)

Specifications of HD64F38024DV

Core Processor

H8/300L

Core Size

8-Bit

Speed

10MHz

Connectivity

SCI

Peripherals

LCD, PWM, WDT

Number Of I /o

51

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F38024DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 969 of 1021

- Download datasheet (5Mb)

g. Optimization Improvement by optimize=variable_access

h. Optimization Improvement by optimize=register

i. Optimization Improvement of Assembly Programs

j. Debugging Information Deletion

k. Debugging Information Compression

2. Added and Improved Functions in Upgrade from Ver. 7.0 to Ver. 8.0

a. Support for New CPU

b. Output to Empty Area

c. Specifying Memory Size Used

d. Specifying 8-bit Absolute Area Address

e. Changing Error Level for Overlapping Section Addresses

Variables allocated in a 16-bit absolute address space can be allocated in an 8-bit address space

by applying optimization.

When option optimize=speed is not specified, the file is compressed after optimizing the

saving and restoring of register contents between functions, and replacing saving and restoring

of multiple register contents with function calls.

Sections including .org, .align, or .data directive can be optimized.

The strip option can be used to delete debugging information from either the load module file

or the library file.

The compress option can be used to compress debugging information.

Input of an object file with a CPU type of H8SX is supported.

The space option can be used to fill the specified value in an empty area.

The memory option specifies the used size of internal memory.

The sbr option specifies the address to locate the 8-bit absolute address area.

The error level for overlapping section addresses at linkage is changed from Fatal in Ver. 7.0

to Error in Ver. 8.0. Thus, even when the section addresses overlap, the change_message

option can be used to continue processing on the user’s own responsibility.

955

Related parts for HD64F38024DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet: