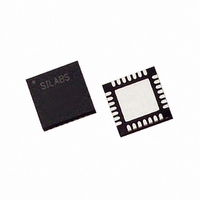

C8051F321 Silicon Laboratories Inc, C8051F321 Datasheet - Page 161

C8051F321

Manufacturer Part Number

C8051F321

Description

IC 8051 MCU 16K FLASH 28MLP

Manufacturer

Silicon Laboratories Inc

Series

C8051F32xr

Datasheet

1.C8051F320R.pdf

(256 pages)

Specifications of C8051F321

Core Processor

8051

Core Size

8-Bit

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART, USB

Peripherals

Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT

Number Of I /o

21

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Ram Size

2.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 13x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

28-VQFN Exposed Pad, 28-HVQFN, 28-SQFN, 28-DHVQFN

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

C8051F321

Manufacturer:

SILICON

Quantity:

249

Part Number:

C8051F321

Manufacturer:

SILICON LABS/芯科

Quantity:

20 000

Company:

Part Number:

C8051F321-GM

Manufacturer:

SiliconL

Quantity:

4 364

Part Number:

C8051F321-GM

Manufacturer:

SILICON LABS/芯科

Quantity:

20 000

Part Number:

C8051F321-GMR

Manufacturer:

SILICON LABS/芯科

Quantity:

20 000

15.9. The Serial Interface Engine

The Serial Interface Engine (SIE) performs all low level USB protocol tasks, interrupting the processor when data has

successfully been transmitted or received. When receiving data, the SIE will interrupt the processor when a complete

data packet has been received; appropriate handshaking signals are automatically generated by the SIE. When trans-

mitting data, the SIE will interrupt the processor when a complete data packet has been transmitted and the appropri-

ate handshake signal has been received.

The SIE will not interrupt the processor when corrupted/erroneous packets are received.

15.10. Endpoint0

Endpoint0 is managed through the USB register E0CSR (Figure 15.20). The INDEX register must be loaded with

0x00 to access the E0CSR register.

An Endpoint0 interrupt is generated when:

The E0CNT register (Figure 15.21) holds the number of received data bytes in the Endpoint0 FIFO.

Bits7-4:

Bit3:

Bit2:

Bit1:

Bit0:

R/W

Bit7

-

1.

bit (E0CSR.0) is set to ‘1’ by hardware.

2.

INPRDY is reset to ‘0’ by hardware.

3.

4.

5.

DATAEND bit (E0CSR.3).

Figure 15.19. CMIE: USB0 Common Interrupt Enable (USB Register)

Unused. Read = 0000b; Write = don’t care.

SOFE: Start of Frame Interrupt Enable

0: SOF interrupt disabled.

1: SOF interrupt enabled.

RSTINTE: Reset Interrupt Enable

0: Reset interrupt disabled.

1: Reset interrupt enabled.

RSUINTE: Resume Interrupt Enable

0: Resume interrupt disabled.

1: Resume interrupt enabled.

SUSINTE: Suspend Interrupt Enable

0: Suspend interrupt disabled.

1: Suspend interrupt enabled.

A data packet (OUT or SETUP) has been received and loaded into the Endpoint0 FIFO. The OPRDY

An IN data packet has successfully been unloaded from the Endpoint0 FIFO and transmitted to the host;

An IN transaction is completed (this interrupt generated during the status stage of the transaction).

Hardware sets the STSTL bit (E0CSR.2) after a control transaction ended due to a protocol violation.

Hardware sets the SUEND bit (E0CSR.4) because a control transfer ended before firmware sets the

R/W

Bit6

-

R/W

Bit5

-

R/W

Bit4

-

SOFE

R/W

Bit3

Rev. 1.1

RSTINTE RSUINTE SUSINTE 00000110

R/W

Bit2

R/W

Bit1

C8051F320/1

R/W

Bit0

USB Address:

Reset Value

0x0B

161