ATMEGA2560R231-AU Atmel, ATMEGA2560R231-AU Datasheet - Page 225

ATMEGA2560R231-AU

Manufacturer Part Number

ATMEGA2560R231-AU

Description

BUNDLE ATMEGA2560/RF231 TQFP

Manufacturer

Atmel

Datasheet

1.ATMEGA640V-8CU.pdf

(444 pages)

Specifications of ATMEGA2560R231-AU

Frequency

2.4GHz

Modulation Or Protocol

802.15.4 Zigbee, 6LoWPAN, RF4CE, SP100, WirelessHART™, ISM

Data Interface

PCB, Surface Mount

Memory Size

256kB Flash, 4kB EEPROM, 8kB RAM

Antenna Connector

PCB, Surface Mount

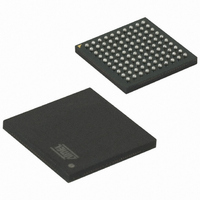

Package / Case

100-TFBGA

Processor Series

ATMEGA256x

Core

AVR8

Data Bus Width

8 bit

Program Memory Type

Flash

Program Memory Size

256 KB

Data Ram Size

8 KB

Development Tools By Supplier

ATAVRRZ541, ATAVRRAVEN, ATAVRRZRAVEN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Voltage - Supply

-

Power - Output

-

Operating Temperature

-

Applications

-

Sensitivity

-

Data Rate - Maximum

-

Current - Transmitting

-

Current - Receiving

-

Lead Free Status / Rohs Status

Details

- Current page: 225 of 444

- Download datasheet (10Mb)

21.9.4

2549M–AVR–09/10

UCSRnC – USART Control and Status Register n C

• Bit 3 – TXENn: Transmitter Enable n

Writing this bit to one enables the USART Transmitter. The Transmitter will override normal port

operation for the TxDn pin when enabled. The disabling of the Transmitter (writing TXENn to

zero) will not become effective until ongoing and pending transmissions are completed, that is,

when the Transmit Shift Register and Transmit Buffer Register do not contain data to be trans-

mitted. When disabled, the Transmitter will no longer override the TxDn port.

• Bit 2 – UCSZn2: Character Size n

The UCSZn2 bits combined with the UCSZn1:0 bit in UCSRnC sets the number of data bits

(Character SiZe) in a frame the Receiver and Transmitter use.

• Bit 1 – RXB8n: Receive Data Bit 8 n

RXB8n is the ninth data bit of the received character when operating with serial frames with nine

data bits. Must be read before reading the low bits from UDRn.

• Bit 0 – TXB8n: Transmit Data Bit 8 n

TXB8n is the ninth data bit in the character to be transmitted when operating with serial frames

with nine data bits. Must be written before writing the low bits to UDRn.

• Bits 7:6 – UMSELn1:0 USART Mode Select

These bits select the mode of operation of the USARTn as shown in

Table 21-4.

Note:

• Bits 5:4 – UPMn1:0: Parity Mode

These bits enable and set type of parity generation and check. If enabled, the Transmitter will

automatically generate and send the parity of the transmitted data bits within each frame. The

Bit

Read/Write

Initial Value

UMSELn1

1. See

0

0

1

1

operation.

UMSELn1

UMSELn Bits Settings

“USART in SPI Mode” on page 232

R/W

7

0

UMSELn0

R/W

UMSELn0

6

0

0

1

0

1

ATmega640/1280/1281/2560/2561

UPMn1

R/W

5

0

UPMn0

R/W

4

0

for full description of the Master SPI Mode (MSPIM)

USBSn

R/W

3

0

Master SPI (MSPIM)

Asynchronous USART

UCSZn1

Synchronous USART

R/W

2

1

(Reserved)

Mode

Table

UCSZn0

R/W

1

1

21-4.

(1)

UCPOLn

R/W

0

0

UCSRnC

225

Related parts for ATMEGA2560R231-AU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

IC AVR MCU 256K 16MHZ 100TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 256K FLASH 16MHZ 100TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 256K FLASH 16MHZ 100CBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 256K FLASH 100-CBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 256K 16MHZ 100TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet: