ATMEGA2560R231-AU Atmel, ATMEGA2560R231-AU Datasheet - Page 226

ATMEGA2560R231-AU

Manufacturer Part Number

ATMEGA2560R231-AU

Description

BUNDLE ATMEGA2560/RF231 TQFP

Manufacturer

Atmel

Datasheet

1.ATMEGA640V-8CU.pdf

(444 pages)

Specifications of ATMEGA2560R231-AU

Frequency

2.4GHz

Modulation Or Protocol

802.15.4 Zigbee, 6LoWPAN, RF4CE, SP100, WirelessHART™, ISM

Data Interface

PCB, Surface Mount

Memory Size

256kB Flash, 4kB EEPROM, 8kB RAM

Antenna Connector

PCB, Surface Mount

Package / Case

100-TFBGA

Processor Series

ATMEGA256x

Core

AVR8

Data Bus Width

8 bit

Program Memory Type

Flash

Program Memory Size

256 KB

Data Ram Size

8 KB

Development Tools By Supplier

ATAVRRZ541, ATAVRRAVEN, ATAVRRZRAVEN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Voltage - Supply

-

Power - Output

-

Operating Temperature

-

Applications

-

Sensitivity

-

Data Rate - Maximum

-

Current - Transmitting

-

Current - Receiving

-

Lead Free Status / Rohs Status

Details

- Current page: 226 of 444

- Download datasheet (10Mb)

2549M–AVR–09/10

Receiver will generate a parity value for the incoming data and compare it to the UPMn setting.

If a mismatch is detected, the UPEn Flag in UCSRnA will be set.

Table 21-5.

• Bit 3 – USBSn: Stop Bit Select

This bit selects the number of stop bits to be inserted by the Transmitter. The Receiver ignores

this setting.

Table 21-6.

• Bit 2:1 – UCSZn1:0: Character Size

The UCSZn1:0 bits combined with the UCSZn2 bit in UCSRnB sets the number of data bits

(Character SiZe) in a frame the Receiver and Transmitter use.

Table 21-7.

• Bit 0 – UCPOLn: Clock Polarity

This bit is used for synchronous mode only. Write this bit to zero when asynchronous mode is

used. The UCPOLn bit sets the relationship between data output change and data input sample,

and the synchronous clock (XCKn).

Table 21-8.

UCPOLn

UCSZn2

0

1

UPMn1

0

0

0

0

1

1

1

1

0

0

1

1

UPMn Bits Settings

USBS Bit Settings

UCSZn Bits Settings

UCPOLn Bit Settings

USBSn

Transmitted Data Changed (Output of

0

1

Falling XCKn Edge

Rising XCKn Edge

UCSZn1

UPMn0

TxDn Pin)

0

0

1

1

0

0

1

1

0

1

0

1

ATmega640/1280/1281/2560/2561

UCSZn0

0

1

0

1

0

1

0

1

Received Data Sampled (Input on RxDn

Enabled, Even Parity

Enabled, Odd Parity

Stop Bit(s)

Parity Mode

Reserved

1-bit

2-bit

Disabled

Falling XCKn Edge

Rising XCKn Edge

Character Size

Pin)

Reserved

Reserved

Reserved

5-bit

6-bit

7-bit

8-bit

9-bit

226

Related parts for ATMEGA2560R231-AU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

IC AVR MCU 256K 16MHZ 100TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 256K FLASH 16MHZ 100TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

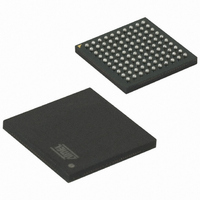

MCU AVR 256K FLASH 16MHZ 100CBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 256K FLASH 100-CBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 256K 16MHZ 100TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet: