CYII4SC014KAA-GTC Cypress Semiconductor Corp, CYII4SC014KAA-GTC Datasheet - Page 2

CYII4SC014KAA-GTC

Manufacturer Part Number

CYII4SC014KAA-GTC

Description

IC SENSOR IMAGE COLOR 49-PGA

Manufacturer

Cypress Semiconductor Corp

Type

CMOS Imagingr

Datasheet

1.CYII4SC014K-EVAL.pdf

(27 pages)

Specifications of CYII4SC014KAA-GTC

Package / Case

49-PGA

Pixel Size

8µm x 8µm

Active Pixel Array

3048H x 4560V

Frames Per Second

3

Voltage - Supply

3.3V

Operating Supply Voltage

3.6 V

Maximum Operating Temperature

+ 50 C

Minimum Operating Temperature

0 C

Image Size

4560 H x 3048 V

Color Sensing

Color

Package

49PGA

Operating Temperature

0 to 50 °C

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Contains lead / RoHS non-compliant

Other names

IBIS4-14000-C

IBIS4-14000-C

IBIS4-14000-C

Ordering Information

Architecture and Operation

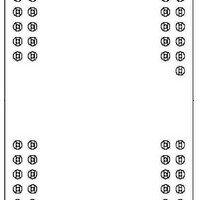

Floor Plan

The basic architecture of the sensor is shown in the

Diagram

arrays. The imager arrays row is selected by the row drivers or

reset by them. There are two Y shift registers, one points at the

row that is read out and the other points at the row to be reset.

The second pointer may lead the first pointer by a specific

number of rows. In that case, the time difference between both

pointers is the integration time. Alternatively, both shift registers

can point at the same row for reset and readout for a faster reset

sequence. When the row is read out, it is also reset. This is to do

double sampling for fixed pattern noise reduction.

The pixel array of the IBIS4-14000 consists of 4536 x 3024 active

pixels and 24 additional columns and rows which can be

addressed (see

pixel information and perform the double sampling operation.

They also multiplex the signals on the readout buses which are

buffered by the output amplifiers.

The shift registers can be configured for various subsampling

modes. The output amplifiers can be individually powered down

and some other extra functions are available. These options are

configurable via a serial input port.

Figure 1. Location of the 24 Additional Columns and Rows,

Scan Direction of the Array

Document #: 38-05709 Rev. *D

CYII4SM014KAA-GEC

CYII4SM014KAA-GECH

CYII4SM014KAA-GWC

CYII4SM014K-EVAL

24 x 4536 dummy pixels

4 analog outputs

Marketing Part Number

on page 1. The Y shift registers point at a row of imager

Figure

------------- SKY --------------

3024 x 4536 active pixels

3048 x 4560 total pixels

Top of camera

1). The column amplifiers read out the

Mono Standard Grade with Glass

Mono High Grade with Glass

Mono Standard Grade without Glass

Mono Demo Kit

3024 x 24 dummy pixels

Logic Block

pixel 0,0

Description

Pixel Specifications

Figure 2. Pixel and Column Structure Schematic

Architecture

The pixel is a classic three transistor active pixel. The photodiode

is a high-fill-factor n-well/p-substrate diode. The chip has

separate power supplies for the following:

■

■

■

FPN and PRNU

Fixed Pattern Noise correction is done on-chip using the Double

Sampling technique. The pixel is read out and this voltage value

is sampled on the capacitor SHS. After read out the pixel is reset

again and this value is sampled by SHR. Both sample and reset

values of each pixel are subtracted in the column amplifiers to

subtract FPN. Raw images taken by the sensor typically feature

a residual (local) FPN of 0.11% RMS of the saturation voltage.

The Photo Response Non Uniformity (PRNU), caused by

mismatch of photodiode node capacitances, is not corrected

on-chip. Measurements indicate that the typical PRNU is less

than1% RMS of the signal level.

RESET

General power supply for the analog image core (VDD)

Power supply for the reset line drivers (VDDR)

Separate power supply for the pixel itself (VDDARRAY).

M1

VDD_ ARRAY

CYII4SM014KAA-GEC

M2

CYII4SC014KAA-GTC

SELECT

M3

SHS

49 pin PGA

Demo Kit

Package

Column

Page 2 of 27

SHR

PC

[+] Feedback