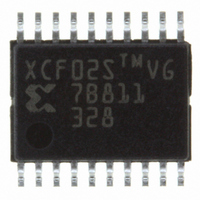

XCF02SVOG20C Xilinx Inc, XCF02SVOG20C Datasheet - Page 2

XCF02SVOG20C

Manufacturer Part Number

XCF02SVOG20C

Description

PROM, PLATFORM FLASH, 2MBIT, 20TSSOP

Manufacturer

Xilinx Inc

Datasheet

1.XCF01SVOG20C.pdf

(35 pages)

Specifications of XCF02SVOG20C

Memory Type

Flash

Memory Size

2Mbit

Clock Frequency

50MHz

Supply Voltage Range

2.3V To 2.7V, 3V To 3.6V

Memory Case Style

TSSOP

No. Of Pins

20

Operating Temperature Range

-40°C To +85°

Programmable Type

In System Programmable

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Package / Case

20-TSSOP (0.173", 4.40mm Width)

Interface Type

Serial, Parallel, JTAG

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

122-1287-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XCF02SVOG20C

Manufacturer:

Xlinx

Quantity:

7

Company:

Part Number:

XCF02SVOG20C

Manufacturer:

XILINX

Quantity:

445

Company:

Part Number:

XCF02SVOG20C

Manufacturer:

XILINX/42

Quantity:

399

Part Number:

XCF02SVOG20C

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

Company:

Part Number:

XCF02SVOG20C0936

Manufacturer:

SIPEX

Quantity:

59 427

Part Number:

XCF02SVOG20CLF

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

X-Ref Target - Figure 1

X-Ref Target - Figure 2FI

When the FPGA is in Master Serial mode, it generates a

configuration clock that drives the PROM. With CF High, a

short access time after CE and OE are enabled, data is

available on the PROM DATA (D0) pin that is connected to

the FPGA DIN pin. New data is available a short access

time after each rising clock edge. The FPGA generates the

appropriate number of clock pulses to complete the

configuration.

When the FPGA is in Slave Serial mode, the PROM and the

FPGA are both clocked by an external clock source, or

optionally, for the XCFxxP PROM only, the PROM can be

used to drive the FPGA’s configuration clock.

The XCFxxP version of the Platform Flash PROM also

supports Master SelectMAP and Slave SelectMAP (or

Slave Parallel) FPGA configuration modes. When the FPGA

is in Master SelectMAP mode, the FPGA generates a

configuration clock that drives the PROM. When the FPGA

is in Slave SelectMAP Mode, either an external oscillator

generates the configuration clock that drives the PROM and

the FPGA, or optionally, the XCFxxP PROM can be used to

drive the FPGA’s configuration clock. With BUSY Low and

CF High, after CE and OE are enabled, data is available on

the PROMs DATA (D0-D7) pins. New data is available a

DS123 (v2.18) May 19, 2010

Product Specification

TCK

TMS

TDI

TDO

OSC

R

TMS

TDO

TCK

TDI

CLK

Interface

Control

JTAG

and

CLK

Interface

CF

Control

JTAG

Figure 1: XCFxxS Platform Flash PROM Block Diagram

Figure 2: XCFxxP Platform Flash PROM Block Diagram

and

CE

CF

CE

Address

Data

Address

Data

REV_SEL [1:0]

Memory

EN_EXT_SEL

Memory

www.xilinx.com

Platform Flash In-System Programmable Configuration PROMs

Data

short access time after each rising clock edge. The data is

clocked into the FPGA on the following rising edge of the

CCLK. A free-running oscillator can be used in the Slave

Parallel/Slave SelectMAP mode.

The XCFxxP version of the Platform Flash PROM provides

additional advanced features. A built-in data decompressor

supports utilizing compressed PROM files, and design

revisioning allows multiple design revisions to be stored on

a single PROM or stored across several PROMs. For design

revisioning, external pins or internal control bits are used to

select the active design revision.

Multiple Platform Flash PROM devices can be cascaded to

support the larger configuration files required when

targeting larger FPGA devices or targeting multiple FPGAs

daisy chained together. When utilizing the advanced

features for the XCFxxP Platform Flash PROM, such as

design revisioning, programming files which span cascaded

PROM devices can only be created for cascaded chains

containing only XCFxxP PROMs. If the advanced XCFxxP

features are not enabled, then the cascaded chain can

include both XCFxxP and XCFxxS PROMs.

Decompressor

Data

OE/RESET

Interface

Serial

OE/RESET

Interface

Parallel

Serial

or

BUSY

DATA (D0)

Serial Mode

CEO

ds123_01_30603

CLKOUT

CEO

DATA (D0)

(Serial/Parallel Mode)

D[1:7]

(Parallel Mode)

DS123_19_031908

2