XCF02SVOG20C Xilinx Inc, XCF02SVOG20C Datasheet - Page 32

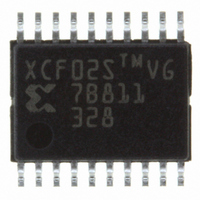

XCF02SVOG20C

Manufacturer Part Number

XCF02SVOG20C

Description

PROM, PLATFORM FLASH, 2MBIT, 20TSSOP

Manufacturer

Xilinx Inc

Datasheet

1.XCF01SVOG20C.pdf

(35 pages)

Specifications of XCF02SVOG20C

Memory Type

Flash

Memory Size

2Mbit

Clock Frequency

50MHz

Supply Voltage Range

2.3V To 2.7V, 3V To 3.6V

Memory Case Style

TSSOP

No. Of Pins

20

Operating Temperature Range

-40°C To +85°

Programmable Type

In System Programmable

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Package / Case

20-TSSOP (0.173", 4.40mm Width)

Interface Type

Serial, Parallel, JTAG

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

122-1287-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XCF02SVOG20C

Manufacturer:

Xlinx

Quantity:

7

Company:

Part Number:

XCF02SVOG20C

Manufacturer:

XILINX

Quantity:

445

Company:

Part Number:

XCF02SVOG20C

Manufacturer:

XILINX/42

Quantity:

399

Part Number:

XCF02SVOG20C

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

Company:

Part Number:

XCF02SVOG20C0936

Manufacturer:

SIPEX

Quantity:

59 427

Part Number:

XCF02SVOG20CLF

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

Revision History

The following table shows the revision history for this document.

DS123 (v2.18) May 19, 2010

Product Specification

04/29/03

06/03/03

11/05/03

11/18/03

12/15/03

05/07/04

Date

R

Version

1.0

1.1

2.0

2.1

2.2

2.3

Xilinx Initial Release.

Made edits to all pages.

Major revision.

Pinout corrections as follows:

•

•

•

• Added specification (4.7kΩ) for recommended pull-up resistor on OE/RESET pin to section

• Added paragraph to section

• Section

• Section

•

• Section

• Section

•

• Section

•

• Section

• Section

• Section

• (Continued on next page)

• Section

• Section

• Section

•

Table

• For VO48 package, removed 38 from VCCINT and added it to VCCO.

• For FS48 package, removed pin D6 from VCCINT and added it to VCCO.

Table 14

• For pin D6, changed name from VCCINT to VCCO.

• For pin A4, changed name from GND to DNC.

Figure 8

"Reset and Power-On Reset Activation," page

and/or buffer on the DONE pin.

itemized features.

descriptive text.

Table 2, page

to tie CF High if it is not tied to the FPGA’s PROG_B (PROGRAM) input.

Figure 6, page

CF pin in each configuration.

Table 12, page

the Low state of CF.

• Revised footnote callout number on T

• Added Footnote (2) callout to T

• Added Typical (Typ) parameter columns and parameters for V

• Added 1.5V operation parameter row to V

• Revised V

• Added parameter row T

• Added parameter row and parameters for parallel configuration mode, ’P’ devices, to I

• Added Footnote (1) and Footnote (2) with callouts in the Test Conditions column for I

• Corrected description for second T

• Revised Footnote (7) to indicate V

• Applied Footnote (7) to second T

Footnote (5)T

Table 14, page

• Added additional state conditions to CLK description.

• Added function of resetting the internal address counter to CF description.

I

CCINTS

13:

"Initiating FPGA Configuration," page 10

"Features," page

"Description," page 1

"Design Revisioning," page

"I/O Input Voltage Tolerance and Power Sequencing," page

"Absolute Maximum Ratings," page

"Supply Voltage Requirements for Power-On Reset and Power-Down," page

"Recommended Operating Conditions," page

"DC Characteristics Over Operating Conditions," page

"AC Characteristics Over Operating Conditions," page

"AC Characteristics Over Operating Conditions When Cascading," page

(VO48 package): For pin 38, changed name from VCCINT to VCCO.

(FS48 package):

, I

CCOS

IH

CYC

3: Updated Virtex®-II configuration bitstream sizes.

16, through

25: Added CF column to truth table, and added an additional row to document

39:

Min, 2.5V operation, from 2.0V to 1.7V.

, and I

Min and T

www.xilinx.com

Platform Flash In-System Programmable Configuration PROMs

CCJS

1: Added package styles and 33 MHz configuration speed limit to

IN

Figure 13, page

CAC

"Standby Mode," page

, to define active and standby mode requirements.

and Max parameters

and following: Added state conditions for CF and BUSY to the

Min formulas.

VCC

CYC

8: Rewritten.

CCO

CAC

.

OER

parameter line.

Revision

= 3.3V.

parameter line to show parameters for 1.8V V

23: Added footnote indicating the directionality of the

13: Revised V

IL

from Footnote (4) to Footnote (3).

11.

and V

and following, five instances: Added instruction

12, concerning use of a pull-up resistor

IH

14:

, ’P’ devices.

IN

and V

16:

15:

CCINT

TS

11: Rewritten.

for ’P’ devices.

and V

CCO

/V

23: Revised

CCJ

13:

.

CCJ

CCO

CCO

,

.

.

32