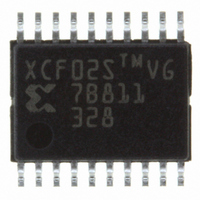

XCF02SVOG20C Xilinx Inc, XCF02SVOG20C Datasheet - Page 24

XCF02SVOG20C

Manufacturer Part Number

XCF02SVOG20C

Description

PROM, PLATFORM FLASH, 2MBIT, 20TSSOP

Manufacturer

Xilinx Inc

Datasheet

1.XCF01SVOG20C.pdf

(35 pages)

Specifications of XCF02SVOG20C

Memory Type

Flash

Memory Size

2Mbit

Clock Frequency

50MHz

Supply Voltage Range

2.3V To 2.7V, 3V To 3.6V

Memory Case Style

TSSOP

No. Of Pins

20

Operating Temperature Range

-40°C To +85°

Programmable Type

In System Programmable

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Package / Case

20-TSSOP (0.173", 4.40mm Width)

Interface Type

Serial, Parallel, JTAG

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

122-1287-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XCF02SVOG20C

Manufacturer:

Xlinx

Quantity:

7

Company:

Part Number:

XCF02SVOG20C

Manufacturer:

XILINX

Quantity:

445

Company:

Part Number:

XCF02SVOG20C

Manufacturer:

XILINX/42

Quantity:

399

Part Number:

XCF02SVOG20C

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

Company:

Part Number:

XCF02SVOG20C0936

Manufacturer:

SIPEX

Quantity:

59 427

Part Number:

XCF02SVOG20CLF

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

Pinouts and Pin Descriptions

The XCFxxS Platform Flash PROM is available in the VO20 and VOG20 packages. The XCFxxP Platform Flash PROM is

available in the VO48, VOG48, FS48, and FSG48 packages. For package drawings, specifications, and additional

information, see UG112, Device Package User Guide, or the

Note:

1. VO20/VOG20 denotes a 20-pin (TSSOP) Plastic Thin Shrink Small Outline Package.

2. VO48/VOG48 denotes a 48-pin (TSOP) Plastic Thin Small Outline Package.

3. FS48/FSG48 denotes a 48-pin (TFBGA) Plastic Thin Fine Pitch Ball Grid Array (0.8 mm pitch).

XCFxxS Pinouts and Pin Descriptions

XCFxxS VO20/VOG20 Pin Names and Descriptions

Table 12

Table 12: XCFxxS Pin Names and Descriptions

DS123 (v2.18) May 19, 2010

Product Specification

D0

CLK

OE/RESET

CE

CF

CEO

TMS

TCK

TDI

Pin Name

provides a list of the pin names and descriptions for the XCFxxS 20-pin VO20/VOG20 package.

R

Scan Order

Boundary

20

19

18

15

22

21

12

11

4

3

0

–

–

–

Boundary-Scan

Output Enable

Output Enable

Output Enable

Output Enable

Mode Select

Function

Data Out

Data Out

Data Out

Data Out

Data In

Data In

Data In

Data In

Clock

D0 is the DATA output pin to provide data for configuring an

FPGA in serial mode. The D0 output is set to a high-

impedance state during ISPEN (when not clamped).

Configuration Clock Input. Each rising edge on the CLK input

increments the internal address counter if the CLK input is

selected, CE is Low, and OE/RESET is High.

Output Enable/Reset (Open-Drain I/O). When Low, this input

holds the address counter reset and the DATA output is in a

high-impedance state. This is a bidirectional open-drain pin

that is held Low while the PROM completes the internal

power-on reset sequence. Polarity is not programmable.

Chip Enable Input. When CE is High, the device is put into

low-power standby mode, the address counter is reset, and

the DATA pins are put in a high-impedance state.

Configuration Pulse (Open-Drain Output). Allows JTAG

CONFIG instruction to initiate FPGA configuration without

powering down FPGA. This is an open-drain output that is

pulsed Low by the JTAG CONFIG command.

Chip Enable Output. Chip Enable Output (CEO) is connected

to the CE input of the next PROM in the chain. This output is

Low when CE is Low and OE/RESET input is High, AND the

internal address counter has been incremented beyond its

Terminal Count (TC) value. CEO returns to High when

OE/RESET goes Low or CE goes High.

JTAG Mode Select Input. The state of TMS on the rising edge

of TCK determines the state transitions at the Test Access

Port (TAP) controller. TMS has an internal 50 kΩ resistive pull-

up to V

driven.

JTAG Clock Input. This pin is the JTAG test clock. It

sequences the TAP controller and all the JTAG test and

programming electronics.

JTAG Serial Data Input. This pin is the serial input to all JTAG

instruction and data registers. TDI has an internal 50 kΩ

resistive pull-up to V

pin is not driven.

www.xilinx.com

CCJ

Platform Flash In-System Programmable Configuration PROMs

to provide a logic 1 to the device if the pin is not

Xilinx Package

CCJ

Pin Description

to provide a logic 1 to the device if the

Specifications.

(VO20/VOG20)

20-pin TSSOP

10

13

1

3

8

7

5

6

4

24