CY7C63743-PXC Cypress Semiconductor Corp, CY7C63743-PXC Datasheet - Page 32

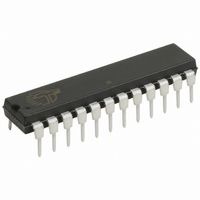

CY7C63743-PXC

Manufacturer Part Number

CY7C63743-PXC

Description

IC MCU 8K USB/PS2 LS 24DIP

Manufacturer

Cypress Semiconductor Corp

Series

enCoRe™r

Specifications of CY7C63743-PXC

Applications

USB Microcontroller

Core Processor

M8B

Program Memory Type

OTP (8 kB)

Controller Series

CY7C637xx

Ram Size

256 x 8

Interface

PS2, USB

Number Of I /o

16

Voltage - Supply

4 V ~ 5.5 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Through Hole

Package / Case

24-DIP (0.300", 7.62mm)

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

428-1621

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY7C63743-PXC

Manufacturer:

TI

Quantity:

12 749

Bit 0: USB Bus Reset - PS/2 Interrupt Enable

Figure 35. Endpoint Interrupt Enable Register

(Address 0x21)

Bit [7:3]: Reserved.

Document #: 38-08022 Rev. *D

Read/Write - - - - -

Bit Name

The function of this interrupt is selectable between detection

of either a USB bus reset condition, or PS/2 activity. The se-

lection is made with the USB-PS/2 Interrupt Mode bit in the

USB Status and Control Register (Figure 14). In either case,

the interrupt will occur if the selected condition exists for 256

μs, and may occur as early as 128 μs.

A USB bus reset is indicated by a single ended zero (SE0) on

the USB D+ and D– pins. The USB Bus Reset interrupt occurs

when the SE0 condition ends. PS/2 activity is indicated by a

continuous LOW on the SDATA pin. The PS/2 interrupt occurs

as soon as the long LOW state is detected.

During the entire interval of a USB Bus Reset or PS/2 interrupt

event, the USB Device Address register is cleared.

The Bus Reset/PS/2 interrupt may occur 128 μs after the bus

condition is removed.

1 = Enable

0 = Disable

Reset

Bit #

7 6 5 4 3

0 0 0 0 0

Reserved

Interrupt

Enable

EP2

R/W

2

0

Interrupt

Enable

EP1

R/W

1

0

Interrupt

Enable

EP0

R/W

0

0

Bit [2:1]: EP2,1 Interrupt Enable

Refer to

Bit 0: EP0 Interrupt Enable

❐

❐

❐

❐

❐

❐

❐

❐

❐

There are two non-control endpoint (EP2 and EP1) interrupts.

If enabled, a non-control endpoint interrupt is generated

when:

1 = Enable

0 = Disable

If enabled, a control endpoint interrupt is generated when:

1 = Enable EP0 interrupt

0 = Disable EP0 interrupt

The USB host writes valid data to an endpoint FIFO. Howev-

er, if the endpoint is in ACK OUT modes, an interrupt is gen-

erated regardless of data packet validity (i.e., good CRC).

Firmware must check for data validity.

The device SIE sends a NAK or STALL handshake packet

to the USB host during the host attempts to read data from

the endpoint (INs).

The device receives an ACK handshake after a successful

read transaction (IN) from the host.

The device SIE sends a NAK or STALL handshake packet

to the USB host during the host attempts to write data (OUTs)

to the endpoint FIFO.

The endpoint 0 mode is set to accept a SETUP token.

After the SIE sends a 0-byte packet in the status stage of a

control transfer.

The USB host writes valid data to an endpoint FIFO. Howev-

er, if the endpoint is in ACK OUT modes, an interrupt is gen-

erated regardless of what data is received. Firmware must

check for data validity.

The device SIE sends a NAK or STALL handshake packet

to the USB host during the host attempts to read data from

the endpoint (INs).

The device SIE sends a NAK or STALL handshake packet

to the USB host during the host attempts to write data (OUTs)

to the endpoint FIFO.

Table 8

for more information.

CY7C63722C

CY7C63723C

CY7C63743C

Page 32 of 53

[+] Feedback