ISD5008SY Nuvoton Technology Corporation of America, ISD5008SY Datasheet - Page 9

ISD5008SY

Manufacturer Part Number

ISD5008SY

Description

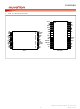

IC VOICE REC/PLAY 4-8MIN 28-SOIC

Manufacturer

Nuvoton Technology Corporation of America

Series

ISD5008r

Datasheet

1.ISD5008EY.pdf

(54 pages)

Specifications of ISD5008SY

Interface

SPI/Microwire

Filter Pass Band

1.7 ~ 3.4kHz

Duration

4 ~ 8 Min

Mounting Type

Surface Mount

Package / Case

28-SOIC (0.300", 7.50mm Width)

For Use With

ISD-ES511 - EVALUATION SYSTEM FOR ISD5100ISD-ES501 - EVALUATION SYSTEM FOR ISD5008

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

PIN NAME

XCLK

RAC

INT

PDIP/SOIC

24

25

26

TSOP

3

4

5

Row Address Clock: RAC is an open drain output pin that

marks the end of a row. At the 8 kHz sampling frequency, the

duration of this period is 200 ms. There are 1,200 rows of

memory in the ISD5008 devices. RAC stays HIGH for 175 ms

and stays LOW for the remaining 25 ms before it reaches the

end of the row.

At the 8 kHz sampling frequency, the RAC pin remains HIGH

for 109.38 µsec and stays LOW for 15.63 µsec under the

Message Cueing mode. See Table 15 Timing Parameters for

RAC timing information at other sample rates. When a record

command is first initiated, the RAC pin remains HIGH for an

extra T

the device. The RAC pin can be used for message

management techniques.

A pull-up resistor is required to connect this pin to other device.

Interrupt:

interrupt pin goes LOW and stays LOW when an Overflow

(OVF), or End of Message (EOM) marker or Message Cueing

is detected. The interrupt is cleared the next time an SPI cycle

is completed. The interrupt status can be read by a RINT

instruction that will give one of the two flags out the MISO line.

A pull-up resistor is required to connect this pin to other device.

OVF Flag. The overflow flag indicates that the end of the

ISD5008’s analog memory has been reached during a record

or playback operation.

EOM Flag. The end of message flag is set only during

playback, when an EOM is found. There are eight possible

EOM markers per row.

External Clock: The external clock input has an internal pull-

down device. Normally, the ISD5008 is operated at one of four

internal rates selected for its internal oscillator by the Sample

Rate Select bits. If greater precision is required, the device can

be clocked through the XCLK pin as described in Table 2.

Because the anti-alising and smoothing filters track the Sample

Rate Select bits, one must, for optimum performance, change

the external clock AND the Sample Rate Configuration bits to

one of the four values properly to set the filters to the correct

cutoff frequency as described in Table 1. The duty cycle on the

input clock is not critical, as the clock is immediately divided by

two internally. If the XCLK is not used, this input should be

connected to V

RACLO

- 9 -

INT is an open drain output pin. The ISD5008

period, to load sample and hold circuits internal to

SSD

.

FUNCTION

Publication Release Date: Oct 31 2008

ISD5008

Revision 1.2