FAN53168MTC FAIRCHILD [Fairchild Semiconductor], FAN53168MTC Datasheet - Page 13

FAN53168MTC

Manufacturer Part Number

FAN53168MTC

Description

6-Bit VID Controlled 2-4 Phase DC-DC Controller

Manufacturer

FAIRCHILD [Fairchild Semiconductor]

Datasheet

1.FAN53168MTC.pdf

(28 pages)

PRODUCT SPECIFICATION

General Description and Applications Information

Theory of Operation

The FAN53168 combines a multi-mode, fixed frequency

PWM control with multi-phase logic outputs for use in 2, 3

and 4 phase synchronous buck CPU core supply power con-

verters. The internal 6-bit VID DAC conforms to Intel’s

VRD/VRM 10 specifications. Multi-phase operation is

important for producing the high currents and low voltages

demanded by today’s microprocessors. Handling the high

currents in a single-phase converter would place high ther-

mal demands on the components in the system such as the

inductors and MOSFETs.

The multi-mode control of the FAN53168 ensures a stable,

high performance topology for:

• Balancing currents and thermals between phases

• High speed response at the lowest possible switching

• Minimizing thermal switching losses due to lower

• Tight load line regulation and accuracy

• High current output from having up to 4 phase operation

• Reduced output ripple due to multi-phase cancellation

• PC board layout noise immunity

• Ease of use and design due to independent component

• Flexibility in operation for tailoring design to low cost or

Number of Phases

The number of operational phases and their phase relation-

ship is determined by internal circuitry which monitors the

PWM outputs. Normally, the FAN53168 operates as a 4-

phase PWM controller. Grounding the PWM4 pin programs

3-phase operation, and grounding the PWM3 and PWM4

pins programs 2-phase operation.

The PWM outputs become logic-level devices once normal

operation starts. The detection is normal and is intended for

driving external gate drivers, such as the FAN53418. Since

each phase is monitored independently, operation approach-

ing 100% duty cycle is possible. Also, more than one output

can be on at a time for overlapping phases.

REV. 1.0.0 6/9/03

frequency and output decoupling

frequency operation

selection

high performance

Ω

Ω

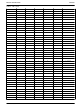

Master Clock Frequency

The clock frequency of the FAN53168 is set with an external

resistor connected from the RT pin to ground. The frequency

follows the graph in TPC 1. To determine the frequency per

phase, the clock is divided by the number of phases in use.

If PWM4 is grounded, then divide the master clock by 3 for

the frequency of the remaining phases. If PWM3 and 4 are

grounded, then divide by 2. If all phases are in use, divide

by 4.

Output Voltage Differential Sensing

The FAN53168 combines differential sensing with a high

accuracy VID DAC and reference and a low offset error

amplifier to maintain a worst-case specification of ±10 mV

differential sensing error with a VID input of 1.6000 V over

its full operating output voltage and temperature range. The

output voltage is sensed between the FB and FBRTN pins.

FB should be connected through a resistor to the regulation

point, usually the remote sense pin of the microprocessor.

FBRTN should be connected directly to the remote sense

ground point. The internal VID DAC and precision reference

are referenced to FBRTN, which has a minimal current of

90µA to allow accurate remote sensing. The internal error

amplifier compares the output of the DAC to the FB pin to

regulate the output voltage.

Output Current Sensing

The FAN53168 provides a dedicated current sense amplifier

(CSA) to monitor the total output current for proper voltage

positioning versus load current and for current limit detec-

tion. Sensing the load current at the output gives the total

average current being delivered to the load, which is an

inherently more accurate method then peak current detection

or sampling the current across a sense element such as the

low side MOSFET. This amplifier can be configured several

ways depending on the objectives of the system:

• Output inductor ESR sensing without thermistor for

• Output inductor ESR sensing with thermistor for

• Sense resistors for highest accuracy measurements

The positive input of the CSA is connected to the CSREF

pin, which is connected to the output voltage. The inputs to

the amplifier are summed together through resistors from the

sensing element (such as the switch node side of the output

inductors) to the inverting input, CSSUM. The feedback

resistor between CSCOMP and CSSUM sets the gain of the

amplifier, and a filter capacitor is placed in parallel with this

resistor. The gain of the amplifier is programmable by adjust-

ing the feedback resistor to set the load line required by the

microprocessor. The current information is then given as the

difference of CSREF –CSCOMP. This difference signal is

used internally to offset the VID DAC for voltage positioning

and as a differential input for the current limit comparator.

lowest cost

improved accuracy with tracking of inductor temperature

FAN53168

13