AC162078 Microchip Technology, AC162078 Datasheet - Page 164

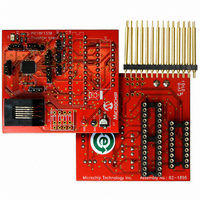

AC162078

Manufacturer Part Number

AC162078

Description

HEADER INTRFC MPLAB ICD2 18F1330

Manufacturer

Microchip Technology

Datasheet

1.AC162078.pdf

(318 pages)

Specifications of AC162078

Accessory Type

Transition Header

Lead Free Status / RoHS Status

Not applicable / Not applicable

For Use With/related Products

ICD2

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Not applicable / Not applicable

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AC162078

Manufacturer:

MICROCHIP

Quantity:

12 000

- Current page: 164 of 318

- Download datasheet (3Mb)

PIC18F1230/1330

15.3

The Master mode indicates that the processor trans-

mits the master clock on the CK line. The Synchronous

Master mode is entered by setting the CSRC bit

(TXSTA<7>). In this mode, the data is transmitted in a

half-duplex manner (i.e., transmission and reception do

not occur at the same time). When transmitting data,

the reception is inhibited and vice versa. Synchronous

mode is entered by setting bit SYNC (TXSTA<4>). In

addition, enable bit, SPEN (RCSTA<7>), is set in order

to configure the TX and RX pins to CK (clock) and DT

(data) lines, respectively.

The Master mode indicates that the processor

transmits the master clock on the CK line. Clock

polarity is selected with the SCKP bit (BAUDCON<4>).

Setting SCKP sets the Idle state on CK as high, while

clearing the bit sets the Idle state as low.

15.3.1

The EUSART transmitter block diagram is shown in

Figure 15-3. The heart of the transmitter is the Transmit

(Serial) Shift Register (TSR). The Shift register obtains

its data from the Read/Write Transmit Buffer register,

TXREG. The TXREG register is loaded with data in

software. The TSR register is not loaded until the last

bit has been transmitted from the previous load. As

soon as the last bit is transmitted, the TSR is loaded

with new data from the TXREG (if available).

FIGURE 15-11:

DS39758D-page 164

RA2/TX/CK pin

Note: Sync Master mode, SPBRG = 0, continuous transmission of two 8-bit words.

(Interrupt Flag)

TXREG Reg

RA3/RX/DT

TRMT bit

TXEN bit ‘

Write to

TXIF bit

( =

EUSART Synchronous

Master Mode

0)

EUSART SYNCHRONOUS MASTER

TRANSMISSION

Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4

1’

Write Word 1

SYNCHRONOUS TRANSMISSION

bit 0

Write Word 2

bit 1

Word 1

bit 2

Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4

status of the TSR register. TRMT is a read-only bit which

Once the TXREG register transfers the data to the TSR

register (occurs in one T

the TXIF flag bit (PIR1<4>) is set. The interrupt can be

enabled or disabled by setting or clearing the interrupt

enable bit, TXIE (PIE1<4>). TXIF is set regardless of

the state of enable bit, TXIE; it cannot be cleared in

software. It will reset only when new data is loaded into

the TXREG register.

While flag bit TXIF indicates the status of the TXREG

register, another bit, TRMT (TXSTA<1>), shows the

is set when the TSR is empty. No interrupt logic is tied to

this bit so the user has to poll this bit in order to

determine if the TSR register is empty. The TSR is not

mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

1.

2.

3.

4.

5.

6.

7.

8.

bit 7

Initialize the SPBRGH:SPBRG registers for the

appropriate baud rate. Set or clear the BRG16

bit, as required, to achieve the desired baud rate.

Enable the synchronous master serial port by

setting bits, SYNC, SPEN and CSRC.

If interrupts are desired, set enable bit, TXIE.

If 9-bit transmission is desired, set bit, TX9.

Enable the transmission by setting bit, TXEN.

If 9-bit transmission is selected, the ninth bit

should be loaded in bit, TX9D.

Start transmission by loading data to the TXREG

register.

If using interrupts, ensure that the GIE and PEIE

bits in the INTCON register (INTCON<7:6>) are

set.

bit 0

Word 2

bit 1

2009 Microchip Technology Inc.

CY

), the TXREG is empty and

bit 7

‘

1’

Related parts for AC162078

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: