QF1DA512-DK Quickfilter Technologies LLC, QF1DA512-DK Datasheet - Page 15

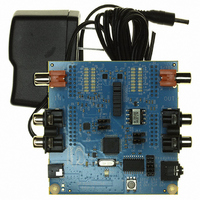

QF1DA512-DK

Manufacturer Part Number

QF1DA512-DK

Description

KIT DEV FOR QF1DA512

Manufacturer

Quickfilter Technologies LLC

Series

SavFIRe™r

Datasheet

1.QF1DA512-QN-T.pdf

(42 pages)

Specifications of QF1DA512-DK

Main Purpose

Filters, Digital Filter Design

Embedded

Yes, ASIC

Utilized Ic / Part

QF1Da512

Primary Attributes

1 512 Tap FIR Filter, 12 ~ 24 Bit

Secondary Attributes

Quickfilter Software Design Tool GUI, Works from 10 ~ 500ksps ADC Data Rates

For Use With

WM2582 - EVALDI EARBUDS TYPE Y686-1006 - BOARD MSP-MOJO + EXPANSION HEADR

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

686-1010

Note: In “SPI Continuous Mode” the value of the dSDO output (lsb) at the end of the data sample will be held constant until

Default operation is to capture on the rising edge of dSCK (SCK for I2S), but this can be changed to capture on falling edge by writing

the DCLK_POL bit in the DCONFIG register (04h). The active polarity of dCS (WS for I2S) is also programmable via the DCONFIG

register (DSEL_POL bit), which is especially useful for applications where the input pins are paired; e.g., dSDI (SD for I2S) and cSDI,

dSCK (SCK for I2S) and cSCK, cCSn and dCS (WS for I2S).

Rev A8 January 7, 2009

dSDO

dSDO

dSDO

dSDO

dSCK

dSCK

dSCK

dSCK

dSDI

dSDI

dSDI

dSDI

dCS

dCS

dCS

dCS

the header is output for the next data sample.

0 to 8 bit header

0 to 8 bit header

0 to 8 bit header

0 to 8 bit header

0 to 8 bit header

0 to 8 bit header

12 to 24 bit input data

12 to 24 bit filtered data

12 to 24 bit input data

12 to 24 bit filtered data

12 to 24 bit input data

12 to 24 bit filtered data

12 to 24 bit input data

12 to 24 bit filtered data

Figure 8: Data Interface Transfer Format

Figure 7: Data Interface Timing Diagram

dclk_pol

dclk_pol

PRELIMINARY DATA SHEET

1

0

0

1

Notes:

> Above waveforms assume a transfer format with dclk_pol = 1

> dSDI capture edge is determined by dclk_pol setting

> dSDO transitions on opposite edge of SDI capture

> dCS active value is set by the dsel_pol bit

> See text for details on header and data size and offset

denotes a “don‟t care”

dSDO

dSDO

dSDO

dSDO

dSCK

dSCK

dSDI

dSDI

dSDI

dSDI

Synchronous Serial Mode

SPI Continuous Mode

SPI Normal Mode

15

I2S Mode

z

z

z

z

0 to 8 bit header

0 to 8 bit header

0 to 8 bit header

0 to 8 bit header

. . .

. . .

. . .

. . .

0 to 8 bit header

0 to 8 bit header

z

z

z

z

. . .

. . .

. . .

. . .

12 to 24 bit input data

12 to 24 bit filtered data

12 to 24 bit input data

12 to 24 bit input data

12 to 24 bit filtered data

12 to 24 bit input data

12 to 24 bit filtered data

12 to 24 bit filtered data

www.quickfiltertech.com

QF1Da512