QF1DA512-DK Quickfilter Technologies LLC, QF1DA512-DK Datasheet - Page 35

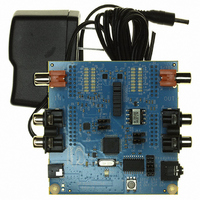

QF1DA512-DK

Manufacturer Part Number

QF1DA512-DK

Description

KIT DEV FOR QF1DA512

Manufacturer

Quickfilter Technologies LLC

Series

SavFIRe™r

Datasheet

1.QF1DA512-QN-T.pdf

(42 pages)

Specifications of QF1DA512-DK

Main Purpose

Filters, Digital Filter Design

Embedded

Yes, ASIC

Utilized Ic / Part

QF1Da512

Primary Attributes

1 512 Tap FIR Filter, 12 ~ 24 Bit

Secondary Attributes

Quickfilter Software Design Tool GUI, Works from 10 ~ 500ksps ADC Data Rates

For Use With

WM2582 - EVALDI EARBUDS TYPE Y686-1006 - BOARD MSP-MOJO + EXPANSION HEADR

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

686-1010

PRELIMINARY DATA SHEET

QF1Da512

13 I2C Option

13.1 Mode of Operation

It is relatively straightforward to interface to and control the QF1Da512 with an Inter-IC (I2C) master. Both I2C and I2S/SPI interface

protocols use a Master/Slave hierarchy and synchronous data transmission, with the I2S/SPI interface using two separate data lines

(one input and one output) and the I2C interface using a single bi-directional data line.

The most significant difference in these two interface mechanisms lies in their addressing schemes. Each I2S/SPI device has its own

chip select (CS) input. The I2S/SPI master selects any given I2S/SPI slave device by activating its chip select (for the QF1Da512,

pulling it low). At any given time, only one I2S/SPI slave will be selected, so any commands sent are responded to by that device. The

I2C interface does not use chip selects. All I2C slave devices receive every command and the addressing scheme, imbedded in the

software protocol, determines which slave is to respond to the command (see figure 19).

Figure 19: I2C Master/Slave Interaction

Each slave must detect its own address and respond only to those commands intended for it. For this reason, the I2C protocol includes

arbitration and collision detection. While an I2S/SPI command is a single stream of bits from the master to the slave (and, for a READ

command, a stream of bits back to the master), an I2C command is a succession of bit-string transfers and Acknowledge/Not-

Acknowledge signals, interspersed throughout the command (see figure 20).

Rev A8 January 7, 2009

35

www.quickfiltertech.com