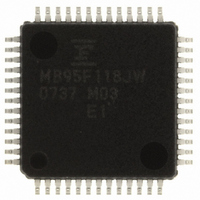

MB95F118JWPMC-GE1 Fujitsu Semiconductor America Inc, MB95F118JWPMC-GE1 Datasheet - Page 39

MB95F118JWPMC-GE1

Manufacturer Part Number

MB95F118JWPMC-GE1

Description

IC MCU 60K FLASH 2KB RAM 52LQFP

Manufacturer

Fujitsu Semiconductor America Inc

Series

F²MC MB95110Mr

Datasheet

1.MB95F118JWPMC-GE1.pdf

(76 pages)

Specifications of MB95F118JWPMC-GE1

Core Processor

F²MC-8FX

Core Size

8-Bit

Speed

16MHz

Connectivity

I²C, LIN, SIO, UART/USART

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

39

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.4 V ~ 5.5 V

Data Converters

A/D 8x8/10b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

52-LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Other names

865-1071

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MB95F118JWPMC-GE1

Manufacturer:

AD

Quantity:

1 000

Company:

Part Number:

MB95F118JWPMC-GE1

Manufacturer:

Fujitsu Semiconductor America Inc

Quantity:

10 000

(2) Source Clock/Machine Clock

*1 : Clock before setting division due to machine clock division ratio selection bit (SYCC : DIV1 and DIV0) . This

*

Source clock

cycle time*

setting division)

Source clock

frequency

Machine clock

cycle time*

instruction

execution time)

Machine clock

frequency

2

(Clock before

(Minimum

• Outline of clock generation block

: Operation clock of the microcontroller. Machine clock can be selected as follows.

Parameter

source clock is divided by the machine clock division ratio selection bit (SYCC : DIV1 and DIV0) , and it

becomes the machine clock. Further, the source clock can be selected as follows.

• Main clock divided by 2

• PLL multiplication of main clock (select from 1, 2, 2.5, 4 multiplication)

• Sub clock divided by 2

• PLL multiplication of sub clock (select from 2, 3, 4 multiplication)

• Source clock (no division)

• Source clock divided by 4

• Source clock divided by 8

• Source clock divided by 16

1

2

(main oscillation)

Sym-

t

(sub oscillation)

t

F

F

bol

F

F

MCLK

SCLK

MPL

SPL

MP

SP

F

F

CH

CL

Condi-

tions

⎯

Devided by 2

Devided by 2

16.384

0.031

1.024

Main PLL

Sub PLL

61.5

0.50

61.5

Min

7.6

7.6

× 2.5

× 1

× 2

× 4

× 2

× 3

× 4

Value

Typ

(Vcc = 5.0 V ± 10%, AVss = Vss = 0.0 V, T

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

131.072

131.072

16.250

( SYCC : SCS1, SCS0 )

32000

16.25

976.5

2000

Clock mode select bit

Max

61.0

( source clock )

MHz When using main clock

MHz When using main clock

SCLK

Unit

kHz When using sub clock

kHz When using sub clock

ns

µs

ns

µs

When using main clock

Min : F

Max : F

When using sub clock

Min : F

Max : F

When using main clock

Min : F

Max : F

When using sub clock

Min : F

Max : F

MB95110M Series

Division

× 1/16

circuit

× 1/4

× 1/8

CH

× 1

CL

SP

SPL

CH

CL

SP

SPL

= 32 kHz, PLL multiplied by 4

= 16.25 MHz, no division

= 8.125 MHz, PLL multiplied by 2

= 32 kHz, divided by 2

= 0.5 MHz, divided by 16

= 1 MHz, divided by 2

= 131 kHz, no division

= 16 kHz, divided by 16

Remarks

( machine clock )

A

= − 40 °C to + 85 °C)

MCLK

39