MC908MR32CFUE Freescale Semiconductor, MC908MR32CFUE Datasheet - Page 55

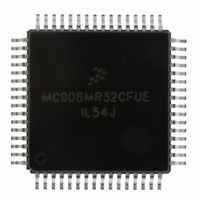

MC908MR32CFUE

Manufacturer Part Number

MC908MR32CFUE

Description

IC MCU 8MHZ 32K FLASH 64-QFP

Manufacturer

Freescale Semiconductor

Series

HC08r

Datasheet

1.MC908MR16CFUE.pdf

(282 pages)

Specifications of MC908MR32CFUE

Core Processor

HC08

Core Size

8-Bit

Speed

8MHz

Connectivity

SCI, SPI

Peripherals

LVD, POR, PWM

Number Of I /o

44

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

768 x 8

Voltage - Supply (vcc/vdd)

4.5 V ~ 5.5 V

Data Converters

A/D 10x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

64-QFP

Processor Series

HC08MR

Core

HC08

Data Bus Width

8 bit

Data Ram Size

768 B

Interface Type

SCI/SPI

Maximum Clock Frequency

8.2 MHz

Number Of Programmable I/os

44

Number Of Timers

6

Operating Supply Voltage

0 V to 5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

FSICEBASE, M68CBL05CE

Minimum Operating Temperature

- 40 C

On-chip Adc

10-ch x 10-bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC908MR32CFUE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MC908MR32CFUE

Manufacturer:

NXP/恩智浦

Quantity:

20 000

- Current page: 55 of 282

- Download datasheet (2Mb)

In 8-bit mode, this 8-bit result register holds the eight MSBs of the 10-bit result. This register is updated

each time an ADC conversion completes. In 8-bit mode, this register contains no interlocking with ADRH.

3.7.4 ADC Clock Register

This register selects the clock frequency for the ADC, selecting between modes of operation.

ADIV2:ADIV0 — ADC Clock Prescaler Bits

Freescale Semiconductor

ADIV2, ADIV1, and ADIV0 form a 3-bit field which selects the divide ratio used by the ADC to generate

the internal ADC clock.

Address:

Address:

Address:

Reset:

Reset:

Reset:

Read:

Read:

Read:

Write:

Write:

Write:

Figure 3-8. ADC Data Register Low (ADRL) Right Justified Mode

Figure 3-9. ADC Data Register Low (ADRL) 8-Bit Mode

ADIV2

$0042

$0042

$0043

Bit 7

AD7

Bit 7

AD9

Bit 7

R

R

R

R

R

0

MC68HC908MR32 • MC68HC908MR16 Data Sheet, Rev. 6.1

Table 3-2

X = don’t care

ADIV2

Figure 3-10. ADC Clock Register (ADCLK)

0

0

0

0

1

= Reserved

= Reserved

= Reserved

ADIV1

AD6

AD8

R

R

6

6

6

0

Table 3-2. ADC Clock Divide Ratio

shows the available clock configurations.

ADIV1

0

0

1

1

X

ADIV0

AD5

AD7

R

R

5

5

5

0

ADIV0

ADICLK

Unaffected by reset

Unaffected by reset

X

0

1

0

1

AD4

AD6

R

R

4

4

4

0

ADC input clock ÷ 1

ADC input clock ÷ 2

ADC input clock ÷ 4

ADC input clock ÷ 8

ADC input clock ÷ 16

MODE1

AD3

AD5

ADC Clock Rate

R

R

3

3

3

0

MODE0

AD2

AD4

R

R

2

2

2

1

AD1

AD3

R

R

1

1

1

0

0

Bit 0

AD0

Bit 0

AD2

Bit 0

R

R

R

0

0

I/O Registers

55

Related parts for MC908MR32CFUE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: