AD9627-125EBZ Analog Devices Inc, AD9627-125EBZ Datasheet - Page 52

AD9627-125EBZ

Manufacturer Part Number

AD9627-125EBZ

Description

12Bit 125 Msps Dual 1.8V PB Free ADC

Manufacturer

Analog Devices Inc

Datasheet

1.AD9627ABCPZ-80.pdf

(76 pages)

Specifications of AD9627-125EBZ

Number Of Adc's

2

Number Of Bits

12

Sampling Rate (per Second)

125M

Data Interface

Serial

Inputs Per Adc

1 Differential

Input Range

2 Vpp

Power (typ) @ Conditions

900mW @ 125MSPS

Voltage Supply Source

Analog and Digital

Operating Temperature

-40°C ~ 85°C

Utilized Ic / Part

AD9627

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

AD9627

DEFAULT OPERATION AND JUMPER SELECTION

SETTINGS

The following is a list of the default and optional settings or

modes allowed on the AD9627 evaluation board.

POWER

Connect the switching power supply that is provided in the

evaluation kit between a rated 100 V ac to 240 V ac wall outlet

at 47 Hz to 63 Hz and P500.

VIN

The evaluation board is set up for a double balun configuration

analog input with optimum 50 Ω impedance matching from

70 MHz to 200 MHz. For more bandwidth response, the differ-

ential capacitor across the analog inputs can be changed or

removed (see Table 13). The common mode of the analog inputs

is developed from the center tap of the transformer via the CML

pin of the ADC (see the Analog Input Considerations section).

VREF

VREF is set to 1.0 V by tying the SENSE pin to ground by adding

a jumper on Header J5 (Pin 1 to Pin 2). This causes the ADC to

operate in 2.0 V p-p full-scale range. To place the ADC in 1.0 V p-p

mode (VREF = 0.5 V), a jumper should be placed on Header J4.

A separate external reference option is also included on the evalua-

tion board. To use an external reference, connect J6 (Pin 1 to Pin 2)

and provide an external reference at TP5. Proper use of the VREF

options is detailed in the Voltage Reference section.

RBIAS

RBIAS requires a 10 kΩ resistor (R503) to ground and is used to

set the ADC core bias current.

CLOCK

The default clock input circuitry is derived from a simple balun-

coupled circuit using a high bandwidth 1:1 impedance ratio balun

(T5) that adds a very low amount of jitter to the clock path. The

clock input is 50 Ω terminated and ac-coupled to handle single-

ended sine wave inputs. The transformer converts the single-ended

input to a differential signal that is clipped before entering the

ADC clock inputs. When the AD9627 input clock divider is

utilized, clock frequencies up to 625 MHz can be input into the

evaluation board through Connector S5.

PDWN

To enable the power-down feature, connect J7, shorting the

PDWN pin to AVDD.

Rev. B | Page 52 of 76

CSB

The CSB pin is internally pulled up, setting the chip into

external pin mode, to ignore the SDIO and SCLK information.

To connect the control of the CSB pin to the SPI circuitry on the

evaluation board, connect J21, Pin 1 to J21, Pin 2.

SCLK/DFS

If the SPI port is in external pin mode, the SCLK/DFS pin sets the

data format of the outputs. If the pin is left floating, the pin is inter-

nally pulled down, setting the default data format condition to

offset binary. Connecting J2, Pin 1 to J2, Pin 2 sets the format to

twos complement. If the SPI port is in serial pin mode, connecting

J2, Pin 2 to J2, Pin 3 connects the SCLK pin to the on-board SPI

circuitry (see the Serial Port Interface (SPI) section).

SDIO/DCS

If the SPI port is in external pin mode, the SDIO/DCS pin sets

the duty cycle stabilizer. If the pin is left floating, the pin is

internally pulled up, setting the default condition to DCS enabled.

To disable the DCS, connect J1, Pin 1 to J1, Pin 2. If the SPI port

is in serial pin mode, connecting J1, Pin 2 to J1, Pin 3 connects

the SDIO pin to the on-board SPI circuitry (see the Serial Port

Interface (SPI) section).

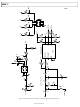

ALTERNATIVE CLOCK CONFIGURATIONS

Two alternate clocking options are provided on the AD9627

evaluation board. The first option is to use an on-board crystal

oscillator (Y1) to provide the clock input to the part. To enable

this crystal, Resistor R8 (0 Ω) and Resistor R85 (10 kΩ) should

be installed, and Resistor R82 and Resistor R30 should be removed.

A second clock option is to use a differential LVPECL clock to

drive the ADC input using the

drive option, the AD9516 charge pump filter components need

to be populated (see Figure 79). Consult the AD9516 data sheet

for more information.

To configure the clock input from S5 to drive the AD9516

reference input instead of directly driving the ADC, the

following components need to be added, removed, and/or

changed.

1.

2.

In addition, unused AD9516 outputs (one LVDS and one LVPECL)

are routed to optional Connector S8 through Connector S11 on

the evaluation board.

Remove R32, R33, R99, and R101 in the default

clock path.

Populate C78 and C79 with 0.001 μF capacitors and

R78 and R79 with 0 Ω resistors in the clock path.

AD9516

(U2). When using this