MT41J256M8HX-125:D Micron Technology Inc, MT41J256M8HX-125:D Datasheet - Page 100

MT41J256M8HX-125:D

Manufacturer Part Number

MT41J256M8HX-125:D

Description

MICMT41J256M8HX-125:D 2GB DDR3 SDRAM

Manufacturer

Micron Technology Inc

Type

DDR3 SDRAMr

Series

-r

Specifications of MT41J256M8HX-125:D

Organization

256Mx8

Address Bus

18b

Maximum Clock Rate

1.066GHz

Operating Supply Voltage (typ)

1.5V

Package Type

FBGA

Operating Temp Range

0C to 95C

Operating Supply Voltage (max)

1.575V

Operating Supply Voltage (min)

1.425V

Supply Current

185mA

Pin Count

78

Mounting

Surface Mount

Operating Temperature Classification

Commercial

Format - Memory

RAM

Memory Type

DDR3 SDRAM

Memory Size

2G (256M x 8)

Speed

800MHz

Interface

Parallel

Voltage - Supply

1.425 V ~ 1.575 V

Operating Temperature

0°C ~ 95°C

Package / Case

78-TFBGA

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MT41J256M8HX-125:D

Manufacturer:

Micron Technology Inc

Quantity:

10 000

Part Number:

MT41J256M8HX-125:D

Manufacturer:

MICRON/美光

Quantity:

20 000

- Current page: 100 of 181

- Download datasheet (9Mb)

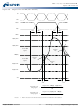

Figure 42: DLL Disable Mode to DLL Enable Mode

PDF: 09005aef826aaadc/Source: 09005aef82a357c3

DDR3_D4.fm - Rev G 2/09 EN

Command

ODT 10

CK#

CKE

CK

ODTL off + 1 × t CK

7

NOP

T0

Notes:

SRE 1

Ta0

10. Static LOW in case R

1. Enter SELF REFRESH.

2. Exit SELF REFRESH.

3. Wait

4. Wait

5. Wait

6. Wait

7. Starting with the idle state.

8. Change frequency.

9. Clock must be stable at least

The clock frequency range for the DLL disable mode is specified by the parameter

t

supported.

DLL disable mode will affect the read data clock to data strobe relationship (

but not the data strobe to data relationship (

line up read data to the controller time domain.

Compared to the DLL on mode where

cycles after the READ command, the DLL disable mode

after the READ command (see Figure 43 on page 101).

WRITE operations function similarly between the DLL enable and DLL disable modes;

however, ODT functionality is not allowed with DLL disable mode.

CK

DLL

t CKSRE

NOP

Ta1

_

t

t

t

t

DIS

XS, then set MR1[0] to “0” to enable DLL.

MRD, then set MR0[8] to “1” to begin DLL RESET.

MRD, update registers (CL, CWL, and write recovery may be necessary).

MOD, any valid command.

. Due to latency counter and timing restrictions, only CL = 6 and CWL = 6 are

Tb0

t CKESR

8

TT

_

NOM

Tc0

100

or R

t

CKSRX.

t CKSRX 9

TT

Tc1

_

WR

t

is enabled; otherwise, static LOW or HIGH.

DQSCK starts from the rising clock edge AL + CL

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SRX 2

Td0

t

DQSQ,

t XS

2Gb: x4, x8, x16 DDR3 SDRAM

MRS 3

Te0

t

QH). Special attention is needed to

t

t MRD

DQSCK starts AL + CL - 1 cycles

Indicates a Break in

Time Scale

MRS 4

Tf0

©2006 Micron Technology, Inc. All rights reserved.

t MRD

t DLLK

MRS 5

Tg0

Commands

t

Don’t Care

DQSCK)

Valid

Valid 6

Th0

Related parts for MT41J256M8HX-125:D

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC SDRAM 64MBIT 133MHZ 54TSOP

Manufacturer:

Micron Technology Inc

Datasheet:

Part Number:

Description:

IC SDRAM 64MBIT 5.5NS 86TSOP

Manufacturer:

Micron Technology Inc

Datasheet:

Part Number:

Description:

IC SDRAM 64MBIT 200MHZ 86TSOP

Manufacturer:

Micron Technology Inc

Datasheet:

Part Number:

Description:

IC SDRAM 64MBIT 133MHZ 54TSOP

Manufacturer:

Micron Technology Inc

Datasheet:

Part Number:

Description:

IC SDRAM 128MBIT 133MHZ 54TSOP

Manufacturer:

Micron Technology Inc

Datasheet:

Part Number:

Description:

IC SDRAM 256MBIT 133MHZ 90VFBGA

Manufacturer:

Micron Technology Inc

Datasheet:

Part Number:

Description:

IC SDRAM 128MBIT 133MHZ 54TSOP

Manufacturer:

Micron Technology Inc

Datasheet:

Part Number:

Description:

IC SDRAM 256MBIT 133MHZ 54TSOP

Manufacturer:

Micron Technology Inc

Datasheet:

Part Number:

Description:

IC DDR SDRAM 512MBIT 6NS 66TSOP

Manufacturer:

Micron Technology Inc

Datasheet:

Part Number:

Description:

IC SDRAM 128MBIT 167MHZ 86TSOP

Manufacturer:

Micron Technology Inc

Datasheet:

Part Number:

Description:

IC SDRAM 128MBIT 143MHZ 86TSOP

Manufacturer:

Micron Technology Inc

Datasheet:

Part Number:

Description:

SDRAM 256M-BIT 1.8V 54-PIN VFBGA

Manufacturer:

Micron Technology Inc

Datasheet:

Part Number:

Description:

IC SDRAM 128MBIT 143MHZ 86TSOP

Manufacturer:

Micron Technology Inc

Datasheet:

Part Number:

Description:

IC SDRAM 128MBIT 125MHZ 54VFBGA

Manufacturer:

Micron Technology Inc

Datasheet:

Part Number:

Description:

IC SDRAM 128MBIT 125MHZ 54VFBGA

Manufacturer:

Micron Technology Inc

Datasheet: