ATF1508ASV-15AU100 Atmel, ATF1508ASV-15AU100 Datasheet - Page 5

ATF1508ASV-15AU100

Manufacturer Part Number

ATF1508ASV-15AU100

Description

IC CPLD 15NS LOW V 100TQFP

Manufacturer

Atmel

Series

ATF1508ASV(L)r

Datasheet

1.ATF1508ASVL-20JU84.pdf

(28 pages)

Specifications of ATF1508ASV-15AU100

Programmable Type

In System Programmable (min 10K program/erase cycles)

Delay Time Tpd(1) Max

15.0ns

Voltage Supply - Internal

3 V ~ 3.6 V

Number Of Macrocells

128

Number Of I /o

80

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

100-TQFP, 100-VQFP

Voltage

3.3V

Memory Type

EEPROM

Number Of Product Terms Per Macro

40

Maximum Operating Frequency

100 MHz

Delay Time

15 ns

Number Of Programmable I/os

80

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Mounting Style

SMD/SMT

Supply Voltage (max)

3.6 V

Supply Voltage (min)

3 V

For Use With

ATF15XX-DK3 - KIT DEV FOR ATF15XX CPLD'S

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Number Of Logic Elements/cells

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ATF1508ASV-15AU100

Manufacturer:

ATMEL

Quantity:

138

Part Number:

ATF1508ASV-15AU100

Manufacturer:

ATMEL/爱特梅尔

Quantity:

20 000

Part Number:

ATF1508ASV-15AU100-T

Manufacturer:

MICROCHIP/微芯

Quantity:

20 000

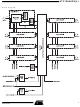

Flip-flop

Figure 1. ATF1508ASV(L) Macrocell

1408H–PLD–7/05

The ATF1508ASV(L)’s flip-flop has very flexible data and control functions. The data

input can come from either the XOR gate, from a separate product term or directly from

the I/O pin. Selecting the separate product term allows creation of a buried registered

feedback within a combinatorial output macrocell. (This feature is automatically imple-

mented by the fitter software). In addition to D, T, JK and SR operation, the flip-flop can

also be configured as a flow-through latch. In this mode, data passes through when the

clock is high and is latched when the clock is low.

The clock itself can either be the Global CLK Signal (GCK) or an individual product term.

The flip-flop changes state on the clock's rising edge. When the GCK signal is used as

the clock, one of the macrocell product terms can be selected as a clock enable. When

the clock enable function is active and the enable signal (product term) is low, all clock

edges are ignored. The flip-flop’s asynchronous reset signal (AR) can be either the Glo-

bal Clear (GCLEAR), a product term, or always off. AR can also be a logic OR of

GCLEAR with a product term. The asynchronous preset (AP) can be a product term or

always off.

ATF1508ASV(L)

5