ATF1508ASV-15AU100 Atmel, ATF1508ASV-15AU100 Datasheet - Page 7

ATF1508ASV-15AU100

Manufacturer Part Number

ATF1508ASV-15AU100

Description

IC CPLD 15NS LOW V 100TQFP

Manufacturer

Atmel

Series

ATF1508ASV(L)r

Datasheet

1.ATF1508ASVL-20JU84.pdf

(28 pages)

Specifications of ATF1508ASV-15AU100

Programmable Type

In System Programmable (min 10K program/erase cycles)

Delay Time Tpd(1) Max

15.0ns

Voltage Supply - Internal

3 V ~ 3.6 V

Number Of Macrocells

128

Number Of I /o

80

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

100-TQFP, 100-VQFP

Voltage

3.3V

Memory Type

EEPROM

Number Of Product Terms Per Macro

40

Maximum Operating Frequency

100 MHz

Delay Time

15 ns

Number Of Programmable I/os

80

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Mounting Style

SMD/SMT

Supply Voltage (max)

3.6 V

Supply Voltage (min)

3 V

For Use With

ATF15XX-DK3 - KIT DEV FOR ATF15XX CPLD'S

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Number Of Logic Elements/cells

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ATF1508ASV-15AU100

Manufacturer:

ATMEL

Quantity:

138

Part Number:

ATF1508ASV-15AU100

Manufacturer:

ATMEL/爱特梅尔

Quantity:

20 000

Part Number:

ATF1508ASV-15AU100-T

Manufacturer:

MICROCHIP/微芯

Quantity:

20 000

Programmable Pin-

keeper Option for

Inputs and I/Os

Speed/Power

Management

1408H–PLD–7/05

The ATF1508ASV(L) offers the option of programming all input and I/O pins so that “pin-

keeper” circuits can be utilized. When any pin is driven high or low and then subse-

quently left floating, it will stay at that previous high- or low-level. This circuitry prevents

unused input and I/O lines from floating to intermediate voltage levels, which causes

unnecessary power consumption and system noise. The keeper circuits eliminate the

need for external pull-up resistors and eliminate their DC power consumption.

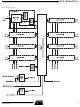

Input Diagram

The ATF1508ASV(L) has several built-in speed and power management features. The

ATF1508ASV(L) contains circuitry that automatically puts the device into a low-power

standby mode when no logic transitions are occurring. This not only reduces power con-

sumption during inactive periods, but also provides proportional power-savings for most

applications running at system speeds below 5 MHz.

To further reduce power, each ATF1508ASV(L) macrocell has a reduced-power bit fea-

ture. This feature allows individual macrocells to be configured for maximum power-

savings. This feature may be selected as a design option.

I/O Diagram

ATF1508ASV(L)

7