EP1S20F672C6 Altera, EP1S20F672C6 Datasheet - Page 189

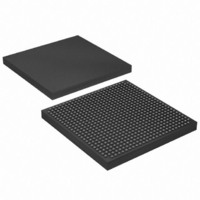

EP1S20F672C6

Manufacturer Part Number

EP1S20F672C6

Description

IC STRATIX FPGA 20K LE 672-FBGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F780C7.pdf

(276 pages)

Specifications of EP1S20F672C6

Number Of Logic Elements/cells

18460

Number Of Labs/clbs

1846

Total Ram Bits

1669248

Number Of I /o

426

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

672-FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Other names

544-1853

EP1S20F672C6

EP1S20F672C6

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP1S20F672C6

Manufacturer:

ALTERA

Quantity:

528

Part Number:

EP1S20F672C6N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 189 of 276

- Download datasheet (4Mb)

Timing Model

Altera Corporation

January 2006

The DirectDrive

predictable performance, accurate simulation, and accurate timing

analysis across all Stratix device densities and speed grades. This section

describes and specifies the performance, internal, external, and PLL

timing specifications.

All specifications are representative of worst-case supply voltage and

junction temperature conditions.

Preliminary & Final Timing

Timing models can have either preliminary or final status. The Quartus II

software issues an informational message during the design compilation

if the timing models are preliminary.

Stratix device timing models.

Preliminary status means the timing model is subject to change. Initially,

timing numbers are created using simulation results, process data, and

other known parameters. These tests are used to make the preliminary

numbers as close to the actual timing parameters as possible.

Final timing numbers are based on actual device operation and testing.

These numbers reflect the actual performance of the device under worst-

case voltage and junction temperature conditions.

Table 4–35. Stratix Device Timing Model Status

EP1S10

EP1S20

EP1S25

EP1S30

EP1S40

EP1S60

EP1S80

Device

™

technology and MultiTrack

Preliminary

Table 4–35

Stratix Device Handbook, Volume 1

DC & Switching Characteristics

™

interconnect ensure

shows the status of the

Final

v

v

v

v

v

v

v

4–19

Related parts for EP1S20F672C6

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: