EP1S20F672C6 Altera, EP1S20F672C6 Datasheet - Page 195

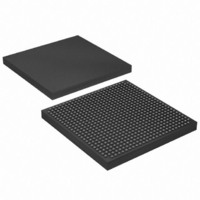

EP1S20F672C6

Manufacturer Part Number

EP1S20F672C6

Description

IC STRATIX FPGA 20K LE 672-FBGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F780C7.pdf

(276 pages)

Specifications of EP1S20F672C6

Number Of Logic Elements/cells

18460

Number Of Labs/clbs

1846

Total Ram Bits

1669248

Number Of I /o

426

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

672-FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Other names

544-1853

EP1S20F672C6

EP1S20F672C6

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP1S20F672C6

Manufacturer:

ALTERA

Quantity:

528

Part Number:

EP1S20F672C6N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 195 of 276

- Download datasheet (4Mb)

Altera Corporation

January 2006

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

M4KDATAAH

M4KADDRASU

M4KADDRAH

M4KDATABSU

M4KDATABH

M4KADDRBSU

M4KADDRBH

M4KDATACO1

M4KDATACO2

M4KCLKHL

M4KCLR

MRAMRC

MRAMWC

MRAMWERESU

MRAMWEREH

MRAMCLKENSU

MRAMCLKENH

MRAMBESU

MRAMBEH

MRAMDATAASU

MRAMDATAAH

MRAMADDRASU

MRAMADDRAH

MRAMDATABSU

Table 4–41. M4K Block Internal Timing Microparameter Descriptions (Part

2 of 2)

Table 4–42. M-RAM Block Internal Timing Microparameter

Descriptions (Part 1 of 2)

Symbol

Symbol

A port data hold time after clock

A port address setup time before clock

A port address hold time after clock

B port data setup time before clock

B port data hold time after clock

B port address setup time before clock

B port address hold time after clock

Clock-to-output delay when using output registers

Clock-to-output delay without output registers

Register minimum clock high or low time. This is a limit on

the min time for the clock on the registers in these blocks.

The actual performance is dependent upon the internal

point-to-point delays in the blocks and may give slower

performance as shown

reported by the timing analyzer in the Quartus II software.

Minimum clear pulse width

Synchronous read cycle time

Synchronous write cycle time

Write or read enable setup time before clock

Write or read enable hold time after clock

Clock enable setup time before clock

Clock enable hold time after clock

Byte enable setup time before clock

Byte enable hold time after clock

A port data setup time before clock

A port data hold time after clock

A port address setup time before clock

A port address hold time after clock

B port setup time before clock

Stratix Device Handbook, Volume 1

inTable 4–36 on page 4–20

Parameter

Parameter

DC & Switching Characteristics

and as

4–25

Related parts for EP1S20F672C6

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: