71V3558S133PF IDT, Integrated Device Technology Inc, 71V3558S133PF Datasheet

71V3558S133PF

Specifications of 71V3558S133PF

Related parts for 71V3558S133PF

71V3558S133PF Summary of contents

Page 1

... The IDT71V3556/58 has an on-chip burst counter. In the burst mode, the IDT71V3556/58 can provide four cycles of data for a single address presented to the SRAM. The order of the burst sequence is defined by the LBO input pin. The LBO pin selects between linear and interleaved burst sequence. The ADV/LD signal is used to load a new external address (ADV/LD = LOW) or increment the internal burst counter (ADV/LD = HIGH) ...

Page 2

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs Symbol Pin Function I Address Inputs ADV/LD Advance / Load I R/W Read / Write I CEN Clock Enable I BW Individual Byte I - Write Enables Chip Enables Chip Enable ...

Page 3

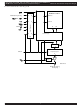

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs LBO Address A [0:16] CE1, CE2, CE2 R/W CEN ADV/LD BWx Clock OE MEMORY ARRAY D Q Address D Q Control D Q Control Logic Clk Gate 6 ...

Page 4

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs LBO Address A [0:17] CE1, CE2, CE2 R/W CEN ADV/LD BWx Clock OE Symbol Parameter Min. V Core Supply Voltage 3.135 DD V I/O Supply Voltage 3 ...

Page 5

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs (1) Grade Temperature V SS Commercial 0°C to +70°C 0V Industrial -40°C to +85°C 0V NOTES the "instant on" case temperature. A 100 DDQ I I I/O ...

Page 6

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs 100 DDQ I I DDQ DDQ DDQ NOTES: 1. Pins 14, 16 and 66 do not have to be connected directly to V the input voltage is V ...

Page 7

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs DDQ I I DDQ I I DDQ DDQ DDQ DDQ I DDQ I DDQ I DDQ N I DDQ NOTES: 1. J3, J5, and R5 do not have to be directly connected and A4 are reserved for future 8M and 16M respectively. 3. DNU = Do not use ...

Page 8

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs CE1 DDQ D I/O I DDQ E I/O I DDQ F I/O I DDQ G I/O I DDQ H V ( I/O I DDQ K I/O I DDQ L I/O I DDQ M I/O I DDQ N I/O ...

Page 9

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs CEN (5) R/W Chip ADV/LD Enable L L Select Select Deselect NOTES Don’t Care When ADV/LD signal is sampled high, the internal burst counter is incremented. The R/W signal is ignored when the counter is advanced. Therefore the nature of the burst cycle (Read or Write) is determined by the status of the R/W signal when the first address is loaded at the beginning of the burst cycle ...

Page 10

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs First Address Second Address Third Address (1) Fourth Address NOTE: 1. Upon completion of the Burst sequence the counter wraps around to its initial state and continues counting. ...

Page 11

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs Cycle Address R/W ADV NOTES defined and High Low Don’t Care High Impedance. ...

Page 12

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs Cycle Address R/W ADV NOTES High Low Don’t Care High Impedance defined and Cycle Address R/W ADV/LD ...

Page 13

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs Cycle Address R/W ADV NOTES High Low Don’t Care High Impedance defined and Cycle Address R/W ADV/ n+1 ...

Page 14

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs Cycle Address R/W ADV NOTES High Low Don’t Care Don’t Know High Impedance defined and Device Outputs are ensured High-Z after the first rising edge of clock upon power-up. ...

Page 15

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs Symbol Parameter |I | Input Leakage Current LI (1) LBO Input Leakage Current | Output Leakage Current LO V Output Low Voltage OL V Output High Voltage OH NOTE: 1 ...

Page 16

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs Symbol Parameter t Clock Cycle Time CYC (1) Clock Frequence t F (2) Clock High Pulse Width t CH (2) Clock Low Pulse Width t CL Output Parameters t Clock High to Valid Data ...

Page 17

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs Commercial and Industrial Temperature Ranges 6. ...

Page 18

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs Commercial and Industrial Temperature Ranges 6. ...

Page 19

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs Commercial and Industrial Temperature Ranges 6. ...

Page 20

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs CEN Commercial and Industrial Temperature Ranges 6. ...

Page 21

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs CS Commercial and Industrial Temperature Ranges 6. ...

Page 22

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs Commercial and Industrial Temperature Ranges 6.42 22 ...

Page 23

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs Commercial and Industrial Temperature Ranges 6.42 23 ...

Page 24

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs Commercial and Industrial Temperature Ranges 6.42 24 ...

Page 25

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs OE OE DATA OUT NOTE read operation is assumed progress. IDT XXXX S XX Device Power Speed Type t OHZ XX X Package Process/ Temperature Range Blank ...

Page 26

... IDT71V3556, IDT71V3558, 128K x 36, 256K x 18, 3.3V Synchronous SRAMS with ZBT Feature, 3.3V I/O, Burst Counter, and Pipelined Outputs 6/30/99 8/23/99 Pg Pg. 6 Pg. 14 Pg. 15 Pg. 22 Pg. 24 10/4/99 Pg. 14 Pg. 15 12/31/99 04/30/00 Pg Pg. 6 Pg. 5,6, 7 Pg. 21 05/26/00 Pg. 23 07/26/00 Pg. 5-8 Pg. 8 Pg. 23 10/25/00 Pg ...