LM49200TLX/NOPB National Semiconductor, LM49200TLX/NOPB Datasheet - Page 14

LM49200TLX/NOPB

Manufacturer Part Number

LM49200TLX/NOPB

Description

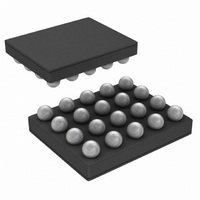

IC AUDIO SUB 1.25W AB 20USMD

Manufacturer

National Semiconductor

Series

Boomer®r

Type

Class ABr

Datasheet

1.LM49200TLNOPB.pdf

(26 pages)

Specifications of LM49200TLX/NOPB

Output Type

2-Channel (Stereo) with Stereo Headphones

Max Output Power X Channels @ Load

1.25W x 2 @ 8 Ohm; 38mW x 2 @ 32 Ohm

Voltage - Supply

2.7 V ~ 5.5 V

Features

Depop, Differential Inputs, I²C, Shutdown, Thermal Protection, Volume Control

Mounting Type

Surface Mount

Package / Case

20-MicroSMD

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

LM49200TLX

www.national.com

Application Information

I

The LM49200 is controlled through an I

interface that consists of a serial data line (SDA) and a serial

clock (SCL). The clock line is uni-directional. The data line is

bi-directional (open drain). The LM49200 and the master can

communicate at clock rates up to 400kHz. Figure 2 shows the

I

stable during the HIGH period of SCL. The LM49200 is a

transmit/receive slave-only device, reliant upon the master to

generate the SCL signal. Each transmission sequence is

framed by a START condition and a STOP condition (Figure

3). Each data word, device address and data, transmitted

over the bus is 8 bits long and is always followed by an ac-

knowledge pulse (Figure 4). The LM49200 device address is

11111000.

I

The LM49200's I

I

age level set by the I

to that of the main power supply pin V

ever logic levels for the I

controller or microprocessor that is operating at a lower

supply voltage than the main battery of a portable system

2

2

2

2

C COMPATIBLE INTERFACE

C interface timing diagram. Data on the SDA line must be

C INTERFACE POWER SUPPLY PIN (I

CV

DD

pin. The LM49200's I

2

C interface is powered up through the

2

CV

DD

2

C interface are dictated by a micro-

pin which can be set independent

2

C interface operates at a volt-

DD

2

. This is ideal when-

C compatible serial

2

CV

FIGURE 3. Start and Stop Diagram

DD

FIGURE 2. I

)

2

C Timing Diagram

14

I

The I

the transition of SDA from HIGH to LOW while SCL is HIGH,

is generated, alerting all devices on the bus that a device ad-

dress is being written to the bus.

The 7-bit device address is written to the bus, most significant

bit (MSB) first, followed by the R/W bit. R/W = 0 indicates the

master is writing to the slave device, R/W = 1 indicates the

master wants to read data from the slave device. Set R/W =

0; the LM49200 is a WRITE-ONLY device and will not re-

spond to the R/W = 1. The data is latched in on the rising edge

of the clock. Each address bit must be stable while SCL is

HIGH. After the last address bit is transmitted, the master de-

vice releases SDA, during which time, an acknowledge clock

pulse is generated by the slave device. If the LM49200 re-

ceives the correct address, the device pulls the SDA line low,

generating an acknowledge bit (ACK).

Once the master device registers the ACK bit, the 8-bit reg-

ister data word is sent. Each data bit should be stable while

SCL is HIGH. After the 8-bit register data word is sent, the

LM49200 sends another ACK bit. Following the acknowl-

edgement of the register data word, the master issues a

STOP bit, allowing SDA to go high while SCL is high.

2

C BUS FORMAT

2

C bus format is shown in Figure 4. The START signal,

30062782

300627s0