tza3005h NXP Semiconductors, tza3005h Datasheet - Page 11

tza3005h

Manufacturer Part Number

tza3005h

Description

Sdh/sonet Stm1/oc3 And Stm4/oc12 Transceiver

Manufacturer

NXP Semiconductors

Datasheet

1.TZA3005H.pdf

(28 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

TZA3005H

Manufacturer:

PHILIPS

Quantity:

14

Company:

Part Number:

TZA3005H

Manufacturer:

MURATA

Quantity:

6 000

Philips Semiconductors

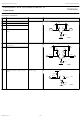

Other operating modes

D

A transmitter-to-receiver loopback mode is available for

diagnostic purposes. When DLEN is LOW, the differential

serial clock and data from the transmitter parallel-to-serial

block continue to be routed to transmitter outputs, but are

also routed to the receiver serial-to-parallel block instead

of the receiver input signals from pins RXSD/RXSDQ and

RXSCLK/RXSCLKQ.

L

A receiver-to-transmitter loopback mode is available for

line testing purposes. When LLEN is LOW, the receiver

input signals (RXSD/RXSDQ and RXSCLK/RXSCLKQ)

are routed, after retiming, to the transmitter output buffers.

The receiver clock and data are also routed to the

serial-to-parallel block.

L

In loop timing mode, the transmitter section is clocked by

the receiver input clock (RXSCLK) instead of by the

internal clock synthesizer. SYNCLKDIV is now derived

from RXSCLK so that it can be used to clock upstream

transmitter logic. Loop timing is enabled by setting pins

ALTPIN, TEST1, TEST2 and TEST3 (see Table 6). After

activating the loop timing mode, the receiver clock must be

synchronized to the transmitter input data

(TXPD0 to TXPD7) by activating master reset (MRST).

In loop timing mode, the internal clock synthesizer is still

used to generate the 19MHz output clock signal on

pin 19MHZO.

2000 Feb 17

INE LOOPBACK

OOP TIMING

IAGNOSTIC LOOPBACK

SDH/SONET STM1/OC3 and STM4/OC12

transceiver

11

S

Some clock recovery devices force their recovered output

clock to zero if a loss of input signal is detected. If this

happens, the SDTTL or SDPECL signals are inactive and

no clock signal is present at pins RXSCLK and RXSCLKQ.

If no clock signal is present at pins RXSCLK/RXSCLKQ,

there is no RXPCLK signal. This may not be suitable for

some applications, in which case, the TZA3005H can be

set to squelched clock operation by setting pins ALTPIN,

TEST1, TEST2 and TEST3 as shown in Table 6.

In squelched clock operation, receiver timing is performed

by a part of the internal clock synthesizer which normally

only provides transmitter timing. This produces a RXPCLK

clock signal when either SDTTL or SDPECL is inactive. If

either SDTTL or SDPECL is inactive in squelched clock

operation, it is equivalent to normal operation. During a

transition from normal operation to squelched clock

operation, the RXPCLK clock cycle exhibits a once-only

random shortening.

Table 6 shows that the same operating mode can be

selected at different settings of the control inputs.

If ALTPIN = 0, the STM4 nibble mode is not available, but

is used for squelched clock operation. If ALTPIN = 1, all

operating modes are available, including STM4 nibble

mode.

QUELCHED CLOCK OPERATION

Product specification

TZA3005H