tza3005h NXP Semiconductors, tza3005h Datasheet - Page 8

tza3005h

Manufacturer Part Number

tza3005h

Description

Sdh/sonet Stm1/oc3 And Stm4/oc12 Transceiver

Manufacturer

NXP Semiconductors

Datasheet

1.TZA3005H.pdf

(28 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

TZA3005H

Manufacturer:

PHILIPS

Quantity:

14

Company:

Part Number:

TZA3005H

Manufacturer:

MURATA

Quantity:

6 000

Philips Semiconductors

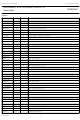

Table 3 ITU reference clock signal (REFCLK) jitter limits

The on-chip PLL contains a phase detector, a loop filter

and a VCO. The phase detector compares the phases of

the VCO and the divided REFCLK signals. The loop filter

converts the phase detector output to a smooth DC voltage

which controls the VCO frequency and ensures that it is

always 622.08 MHz. In STM1/OC3 mode, the correct

output frequency at TXSCLK is obtained by dividing the

VCO frequency by 4. The loop filter parameters are

optimized for minimal output jitter.

CLOCK DIVIDER

The clock divider generates either a byte rate or a nibble

rate version of the serial output clock (TXSCLK) which is

output on pin SYNCLKDIV (see Table 4).

Table 4 SYNCLKDIV frequency

SYNCLKDIV is intended for use as a byte speed clock for

upstream multiplexing and overhead processing circuits.

Using SYNCLKDIV for upstream circuits ensures a stable

frequency and phase relationship is maintained between

the data in to and out of the TZA3005H.

For parallel-to-serial data conversion, the parallel input

data is transferred from the TXPCLK byte clock timing

domain to the internally generated bit clock timing domain.

The internally generated bit clock does not have to be

phase aligned to the TXPCLK signal but must be

synchronized by the master reset (MRST) signal.

Receiver operation

The receiver section of the TZA3005H converts

STM1/OC3 or STM4/OC12 bit-serial input data to a

parallel data output format. In byte mode, input data rates

of 155.52 or 622.08 Mbits/s are converted to an output

data rate of either 19.44 or 77.76 Mbytes/s. In nibble

2000 Feb 17

MODE

INPUT

SDH/SONET STM1/OC3 and STM4/OC12

transceiver

0

0

1

1

MAXIMUM JITTER OF REFCLK

0 (nibble)

1 (byte)

0 (nibble)

1 (byte)

BUSWIDTH

12 kHz TO 1 MHz

56 ps (RMS)

14 ps (RMS)

38.88 MHz

19.44 MHz

155.52 MHz

77.76 MHz

FREQUENCY

SYNCLKDIV

STM1/OC3

STM4/OC12

STM1/OC3

STM1/OC3

STM4/OC12

STM4/OC12

OPERATING

OPERATING

MODE

MODE

8

mode, a 4-bit parallel data stream is generated having a

clock frequency of either 38.88 or 155.52 MHz. It also

provides diagnostic loopback (transmitter to receiver), line

loopback (receiver to transmitter) and squelched clock

operation (transmitter clock to receiver).

F

The frame and byte boundary detection circuit searches

the incoming data for the correct 48-bit frame pattern

which is a sequence of three consecutive A1 bytes of F0 H

followed immediately by three consecutive A2 bytes of

28 H. Frame pattern detection is enabled and disabled by

the out-of-frame enable input (OOF). Detection is enabled

by a rising edge on pin OOF, and remains enabled while

the level on pin OOF is HIGH. It is disabled when at least

one frame pattern is detected and the level on pin OOF is

no longer HIGH. When frame pattern detection is enabled,

the frame pattern is used to locate byte and frame

boundaries in the incoming data stream (Received Serial

Data (RXSD) or looped transmitter data). The serial to

parallel converter block uses the located byte boundary to

divide the incoming data stream into bytes for output on

the parallel output data bus (RXPD0 to RXPD7). When the

correct 48-bit frame pattern is detected, the occurrence of

the frame boundary is indicated by the Frame Pulse (FP)

signal. When frame pattern detection is disabled, the byte

boundary is fixed, and only frame patterns which align with

the fixed byte boundary produce an output on pin FP.

It is extremely unlikely that random data in an STM1/OC3

or STM4/OC12 data stream will replicate the 48-bit frame

pattern. Therefore, the time taken to detect the beginning

of the frame should be less than 250 s (as specified in

“ITU G.783” ) even at extremely high bit error rates.

Once down-stream overhead circuits verify that frame and

byte synchronization are correct, OOF can be set LOW to

prevent the frame search process synchronizing to a

mimic frame pattern.

S

The serial-to-parallel converter causes a delay between

the first bit of an incoming serial data byte to the start of the

parallel output of that byte. The delay depends on the time

taken for the internal parallel load timing circuit to

synchronize the data byte boundaries to the falling edge of

RXPCLK. The timing of RXPCLK is independent of the

byte boundaries. RXPCLK is neither truncated nor

extended during reframe sequences.

RAME AND BYTE BOUNDARY DETECTION

ERIAL

-

TO

-

PARALLEL CONVERTER

Product specification

TZA3005H