tza3005h NXP Semiconductors, tza3005h Datasheet - Page 12

tza3005h

Manufacturer Part Number

tza3005h

Description

Sdh/sonet Stm1/oc3 And Stm4/oc12 Transceiver

Manufacturer

NXP Semiconductors

Datasheet

1.TZA3005H.pdf

(28 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

TZA3005H

Manufacturer:

PHILIPS

Quantity:

14

Company:

Part Number:

TZA3005H

Manufacturer:

MURATA

Quantity:

6 000

Philips Semiconductors

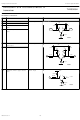

Table 6 Truth table operating modes

Note

1. SD denotes either pin 22 (SDTTL) or pin 23 (SDPECL) (signal present = active = 1; loss of signal = inactive = 0).

Receiver frame alignment

Figure 3 shows a typical frame and boundary alignment

sequence. Frame and byte boundary detection is enabled

on the rising edge of OOF and remains enabled while OOF

is HIGH. Byte boundaries are recognized after the third A2

byte is received. FP goes HIGH for one RXPCLK cycle to

indicate that this is the first data byte with the correct byte

alignment on the output parallel data bus

(RXPD0 to RXPD7).

When interfaced with a section terminating device, OOF

must remain HIGH for a full frame period after the initial

frame pulse (FP). This is to allow the section terminating

device to internally verify that frame and byte alignment

are correct (see Fig.4). Because at least one frame pattern

will have been detected since the rising edge of OOF,

boundary detection is disabled when OOF goes LOW.

2000 Feb 17

0

0

0

0

0

1

1

1

1

X

X

(pin 50)

ALTPIN

SDH/SONET STM1/OC3 and STM4/OC12

transceiver

During a loss of signal, the outputs RXPD0 to RXPD7 are forced to zero (see Table 5).

X

X

X

X

X

0

0

0

0

X

X

(pin 10)

TEST1

X

X

X

X

X

0

0

1

1

X

X

(pin 11)

TEST2

0

0

0

0

1

0

1

0

0

X

X

(pin 13)

TEST3

X

0

0

1

X

X

X

X

X

X

X

BUSWIDTH

(pin 30)

(pin 49)

0

1

1

1

X

X

X

X

X

X

X

MODE

12

The frame and byte boundary detection block is activated

on the rising edge of OOF, and remains active until a frame

pulse (FP) occurs and OOF goes LOW, whichever occurs

last. Figure 4 shows a typical OOF timing pattern when the

TZA3005H is connected to a down stream section

terminating device. OOF stays HIGH for one full frame

after the first frame pulse (FP). The frame and byte

boundary detection block is active until OOF goes LOW.

Figure 5 shows frame and byte boundary detection

activated on the rising edge of OOF, and deactivated by

the first frame pulse (FP) after OOF goes LOW.

X

0

1

X

X

X

X

0

1

X

X

SD

(1)

(pin 31)

1

1

1

1

1

1

1

1

1

X

0

LLEN

(pin 32)

1

1

1

1

1

1

1

1

1

0

X

DLEN

normal operation

(STM1 byte/nibble)

squelched clock

operation

(STM4 byte)

normal operation

(STM4 byte)

normal operation

(STM4 byte)

loop timing

normal operation

loop timing

squelched clock

operation

normal operation

diagnostic loopback

line loopback

OPERATING MODE

Product specification

FUNCTIONAL

TZA3005H