ISL6218CVZA-T Intersil, ISL6218CVZA-T Datasheet

ISL6218CVZA-T

Specifications of ISL6218CVZA-T

Related parts for ISL6218CVZA-T

ISL6218CVZA-T Summary of contents

Page 1

... PART NUMBER ISL6218CV* ISL 6218CV ISL6218CVZ* (Note) ISL 6218CVZ ISL6218CVZA* (Note) ISL 6218CVZ ISL6218CRZ* (Note) ISL62 18CRZ *Add “-T” suffix for tape and reel. Please refer to TB347 for details on reel specifications. NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations ...

Page 2

Pinouts EN DRSEN DSEN VID0 VID1 VID2 VID3 VID4 VID5 PGOOD 2 ISL6218 ISL6218 (38 LD TSSOP) TOP VIEW VDD 1 38 DACOUT 2 37 DSV 3 36 FSET DRSEN 7 32 ...

Page 3

... Thermal Resistance (Typical) TSSOP Package (Note QFN Package (Notes Maximum Operating Junction Temperature +125°C Maximum Storage Temperature Range . . . . . . . . . .-65°C to +150°C Pb-free reflow profile . . . . . . . . . . . . . . . . . . . . . . . . . .see link below http://www.intersil.com/pbfree/Pb-FreeReflow.asp = 5V -10°C to +85°C, Unless Otherwise Specified TEST CONDITIONS = 243k, ±1% ...

Page 4

Electrical Specifications Operating Conditions: V PARAMETER ISEN Full Scale Input Current Overcurrent Threshold ROCSET = 110k (see Figure 10) Soft-Start Current SOFT = 0V Droop Current ISEN = 32µA GATE DRIVER UGATE Source Resistance 500mA Source Current UGATE Source Current ...

Page 5

Functional Pin Description 38 Ld TSSOP VDD 1 DACOUT 2 DSV 3 FSET DRSEN 7 DSEN 8 VID0 9 VID1 10 ISL6218 VID2 11 VID3 12 VID4 13 VID5 14 PGOOD 15 EA+ 16 COMP ...

Page 6

VID0, VID1, VID2, VID3, VID4, VID5 These pins are used as inputs to the 6-bit Digital-to-Analog converter (DAC). VID0 is the least significant bit and VID5 is the most significant bit. UG This pin is the gate drive output to ...

Page 7

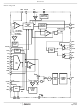

Block Diagram VSEN PGOOD + OVP - 112% RISING 102% FALLING 88% RISING 84% FALLING - + UV 32 COUNT CLOCK CYCLE DACOUT VSOFT SOFT- SOFT START EA+ VID0 VID1 VID2 VID VID3 D/A VID4 VID5 COMP FB 1.75V OCSET ...

Page 8

... The ISL6218 PGOOD pin is both an input and an output. The system signal IMVP4_PWRGD is connected to power good signals from the Vccp and Vcc_mch supplies. The Intersil ISL6225 Dual Voltage Regulator is an ideal choice for the Vccp and Vcc_mch supplies. Refer to Figure 2 and Figure 4. Once the output voltage is within the “ ...

Page 9

The choice of value for soft-start capacitor is determined by the maximum slew rate required for the application. An example calculation is shown in Equation 1. Using the I1 current source on the SOFT pin as 130µA, and the slew ...

Page 10

TABLE 1. INTEL IMPV-IV VID CODES (Continued) VID5 VID4 VID3 VID2 VID1 ...

Page 11

VID[0..5] CURRENT VID CODE CURRENT VOLTAGE LEVEL V CC_CORE PGOOD HIGH FIGURE 5. PLOT SHOWING TIMING OF VID CODE CHANGES AND CORE VOLTAGE SLEWING AS WELL AS PGOOD MASKING VID[0..5] STP_CPU (DSEN) VID COMMAND VOLTAGE V CC_CORE FIGURE 6. CORE ...

Page 12

MOSFET. This “Three-State” mode will hold both upper and low side MOSFETs off during the time that the Low Side MOSFET would normally be on. This “Diode Emulation” is initiated when the current, as sensed ...

Page 13

... PGOOD logic HIGH signals from the Vccp and Vcc_mch regulators. The Intersil ISL6225 is a perfect choice for these two supplies dual regulator and has independent PGOOD functions for each supply. Once these two supplies ...

Page 14

The ISL6218 controller regulates the CORE output voltage to the VID command and once the timer has expired, the PGOOD output is allowed to go high. Note, the PGOOD functions of the V CC_CORE Vcc_mch regulators are wire OR’d together ...

Page 15

ERROR AMPLIFIER - EA ERROR1 R DROOP V DROOP I DROOP + SOFT IMVP IV REFERENCE C SOFT ISL6218 FIGURE 10. SIMPLIFIED BLOCK DIAGRAM OF THE ISL6218 VOLTAGE AND CURRENT CONTROL LOOPS FOR ...

Page 16

Processor power pins; they are placed carefully so they do not to add inductance in the circuit board traces, which could cancel the usefulness of these low inductance components. Specialized low-ESR capacitors intended for switching regulator applications are ...

Page 17

VDD 1.2k__1% DACOUT DSV FSET NC VR_ON EN DRSEN DPSLP DSEN VID0 VID1 VID VID2 VID3 VID4 VID5 PGOOD EA+ COMP 4.64k_1% FB SOFT 3300pF 0.012µF 14k_1% 1800pF No-POP No-POP 3.57k_1% ANALOG FIGURE 12. TYPICAL ...

Page 18

Package Outline Drawing L40.6x6 40 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 3, 10/06 6.00 6 PIN 1 INDEX AREA (4X) 0.15 TOP VIEW ( TYP ) ( TYPICAL RECOMMENDED LAND PATTERN 18 ...

Page 19

... Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use ...