ISL6539IAZ-T Intersil, ISL6539IAZ-T Datasheet - Page 9

ISL6539IAZ-T

Manufacturer Part Number

ISL6539IAZ-T

Description

IC CTRLR DDR DRAM, SDRAM 28QSOP

Manufacturer

Intersil

Datasheet

1.ISL6539CAZ.pdf

(20 pages)

Specifications of ISL6539IAZ-T

Applications

Controller, DDR DRAM, SDRAM

Voltage - Input

3.3 ~ 18 V

Number Of Outputs

2

Voltage - Output

0.9 ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

28-QSOP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

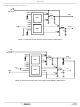

Theory of Operation

Operation

The ISL6539 is a dual channel PWM controller intended for

use in power supplies for graphic chipsets, SDRAM, DDR

DRAM, or other power applications. The IC integrates two

control circuits for two synchronous buck converters. The

output voltage of each controller can be set in the range of

0.9V to 5.5V by an external resistive divider.

The synchronous buck converters can operate from either

an unregulated DC source with a voltage ranging from 5.0V

to 15V, or from a regulated system rail of 3.3V or 5V. In either

operational mode the controller is biased from the +5V

source.

The controllers operate in the current mode with input

voltage feed-forward which simplifies feedback loop

compensation and rejects input voltage variation. An

integrated feedback loop compensation dramatically

reduces the number of external components.

The ISL6539 has a special means to rearrange its internal

architecture into a complete DDR solution. When the DDR

pin is set high, the second channel can provide the capability

to track the output voltage of the first channel. The buffered

reference voltage required by DDR memory chips is also

provided.

Initialization

The ISL6539 initializes if at least one of the enable pins is

set high. The Power-On Reset (POR) function continually

monitors the bias supply voltage on the VCC pin, and

initiates soft-start operation when EN1 or EN2 is high after

the input supply voltage exceeds 4.45V. Should this voltage

drop lower than 4.14V, the POR disables the chip.

Soft-Start

When soft-start is initiated, the voltage on the SOFT pin of

the enabled channel starts to ramp up gradually with the

internal 5µA current charging the soft-start capacitor. The

output voltage follows the soft-start voltage.

When the SOFT pin voltage reaches 0.9V, the output voltage

comes into regulation. When the SOFT voltage reaches

1.5V, the power good (PGOOD) is enabled. The soft-start

process is depicted in Figure 5.

9

ISL6539

Even though the soft-start pin voltage continues to rise after

reaching 1.5V, this voltage does not affect the output

voltage.

The soft-start time (the time from the moment when EN

becomes high to the moment when PGOOD is reported) is

determined by Equation 1:

The time it takes the output voltage to come into regulation

can be obtained from Equation 2:

During soft-start, before the PGOOD pin is enabled, the

undervoltage protection is prohibited. The overvoltage and

overcurrent protection functions are enabled.

If the output capacitor has residue voltage before start-up,

both lower and upper MOSFETs are in off-state until the

soft-start capacitor charges equal the VSEN pin voltage.

This will ensure the output voltage starts from its existing

voltage level.

Output Voltage Program

The output voltage of either channel is set by a resistive

divider from the output to ground. The center point of the

divider is connected to the VSEN pin as shown in Figure 6.

The output voltage value is determined by Equation 3.

where 0.9V is the value of the internal reference. The VSEN

pin voltage is also used by the controller for the power good

function and to detect undervoltage and overvoltage

conditions.

T

T

V

S OFT

R ISE

O

=

3

1

2

4

0.9 V

--- --- --- --- --- --- --- --- --- --- --- --- --- --- --- -

=

=

Ch1 5.0V

Ch3 1.0V

0.6 T

1.5 V C sof t

--- --- --- --- -- --- --- --- --- --- --- --

•

×

(

R 2

R1

5μ A

0.9V

PGOOD

×

SOFT

+

EN

VOUT

1.5V

R 2

FIGURE 5. START-UP

)

Ch2 2.0V

Ch4 5.0V

SOF T

M1.00ms

April 29, 2010

(EQ. 1)

FN9144.6

(EQ. 2)

(EQ. 3)